CPU(Central Processing Unit,中央处理器)

内存(Random Access Memory,随机存取存储器)

缓存(Cache)

CPU、内存和缓存之间有着密切的关系,它们共同构成了计算机系统的核心部分,CPU和内存都具有相应的速率和带宽。在配置电脑过程中,根据CPU的速率和带宽,来搭配相应速率和带宽的内存会直接影响整机的性能,如果搭配不当往往会浪费CPU或内存的性能。

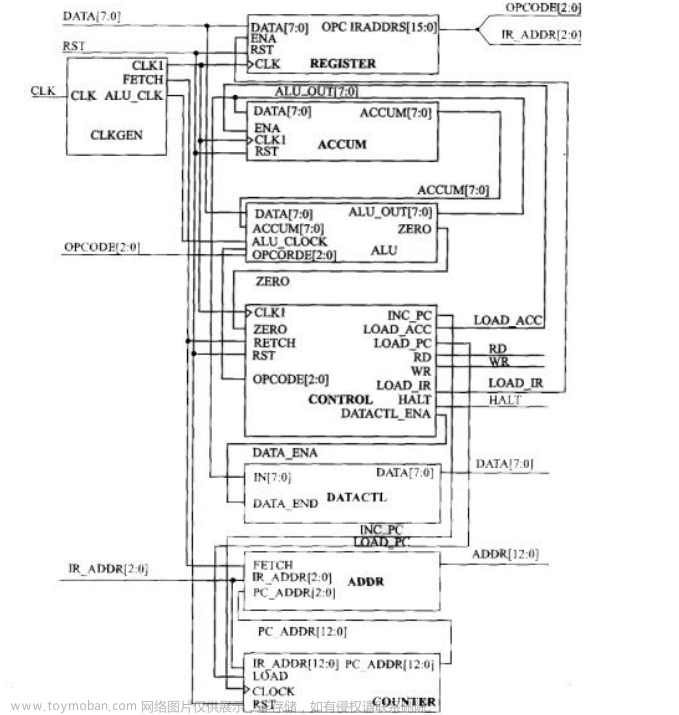

一、CPU是计算机的主要处理器,它执行指令并进行算术、逻辑和控制操作。它是计算机的"大脑",负责处理数据和执行各种任务。

二、内存是计算机中的一种存储设备,用于临时存储和读取数据。CPU从内存中读取指令和数据,并将计算结果写回内存。内存的大小决定了计算机可以同时处理的数据量。

(1)内存用于暂时存放CPU中的运算数据,以及与硬盘等外部存储器交换的数据。它是外存与CPU进行沟通的桥梁,内存的运行决定计算机整体运行快慢。

(2)缓冲区(Buffer)是内存空间的一部分,在内存中预留了一定的存储空间,用来暂时保存输入和输出等I/O操作的数据,这部分预留的空间就叫做缓冲区,且缓冲区是有大小的。 为了达到最佳的磁盘操作效率,可以把需要写入到磁盘的数据先在缓冲区中缓存起来,在缓冲区满了的时候才真正写入到磁盘中,这样就可以减少磁盘IO次数。

三、缓存是位于CPU和内存之间的一种高速存储器。它的目的是加快CPU对数据的访问速度。由于内存的访问速度比CPU慢得多,缓存的存在可以减少CPU等待数据的时间。缓存分为多级,通常包括一级缓存(L1 Cache)、二级缓存(L2 Cache)和三级缓存(L3 Cache)。它们按照容量和访问速度递减的方式排列,以提供更快的数据访问。

(1)内存缓存(from memory cache):将编译解析后的文件,直接存入该进程的内存中,占据该进程一定的内存资源,以方便下次运行使用时的快速读取,一旦该进程关闭,则该进程的内存则会清空。

(2)硬盘缓存(from disk cache):将缓存写入硬盘文件中,读取缓存需要对该缓存存放的硬盘文件进行I/O操作,然后重新解析该缓存内容,读取复杂,速度比内存缓存慢。

Q:为什么要引入缓冲区?

高速设备与低速设备的不匹配,势必会让高速设备花时间等待低速设备,因此需要在这两者之间设立一个缓冲区。

Q:缓存(cache)与缓冲(buffer)的主要区别?

Buffer的核心作用是用来缓冲,缓和冲击。Cache的核心作用是加快取用的速度。简单来说就是buffer偏重于写,而cache偏重于读。

1.容量与速度

容量:网络存储(云存储)>硬盘>内存>缓存>寄存器

速度:寄存器>缓存>内存>硬盘>网络存储(云存储)

在理论上,物理内存太大反而会减慢速度,因为它增加了寻址的时间。

2.缓存是为了解决CPU速度和内存速度的速度差异问题

CPU存取数据的速度非常的快,一秒钟能够存取、处理十亿条指令和数据(术语:CPU主频1G),而内存就慢很多,快的内存能够达到几十兆就不错了,可见两者的速度差异是多么的大 。

内存中被CPU访问最频繁的数据和指令被复制入CPU中的缓存,这样CPU只要到缓存中去取就行了,而缓存的速度要比内存快很多 。

这里要特别指出的是:

1.因为缓存只是内存中少部分数据的复制品,所以CPU到缓存中寻找数据时,也会出现找不到的情况(因为这些数据没有从内存复制到缓存中去),这时CPU还是会到内存中去找数据,这样系统的速度就慢下来了,不过CPU会把这些数据复制到缓存中去,以便下一次不要再到内存中去取。

2.因为随着时间的变化,被访问得最频繁的数据不是一成不变的,也就是说,刚才还不频繁的数据,此时已经需要被频繁的访问,刚才还是最频繁的数据,现在又不频繁了,所以说缓存中的数据要经常按照一定的算法来更换,这样才能保证缓存中的数据是被访问最频繁的。

3.关于一级缓存和二级缓存

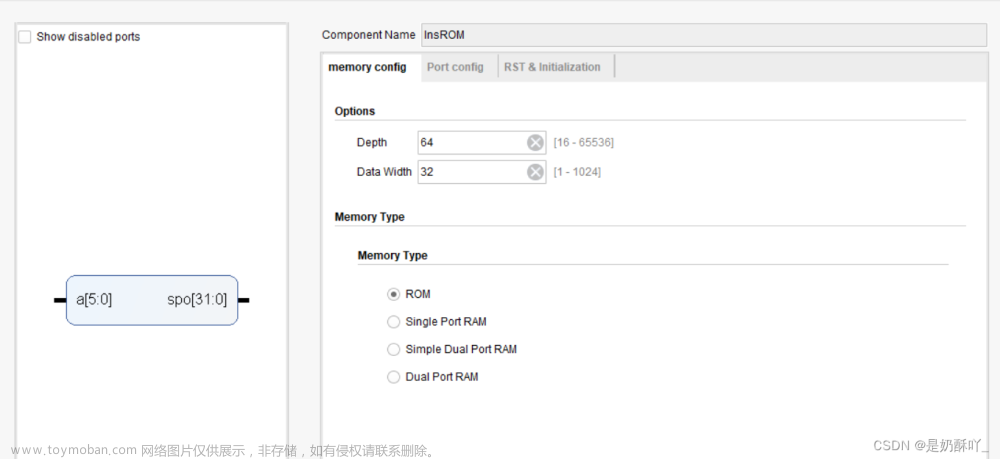

RAM和ROM相对的,RAM是带电存储,即断电信息就消失,ROM则不受影响。

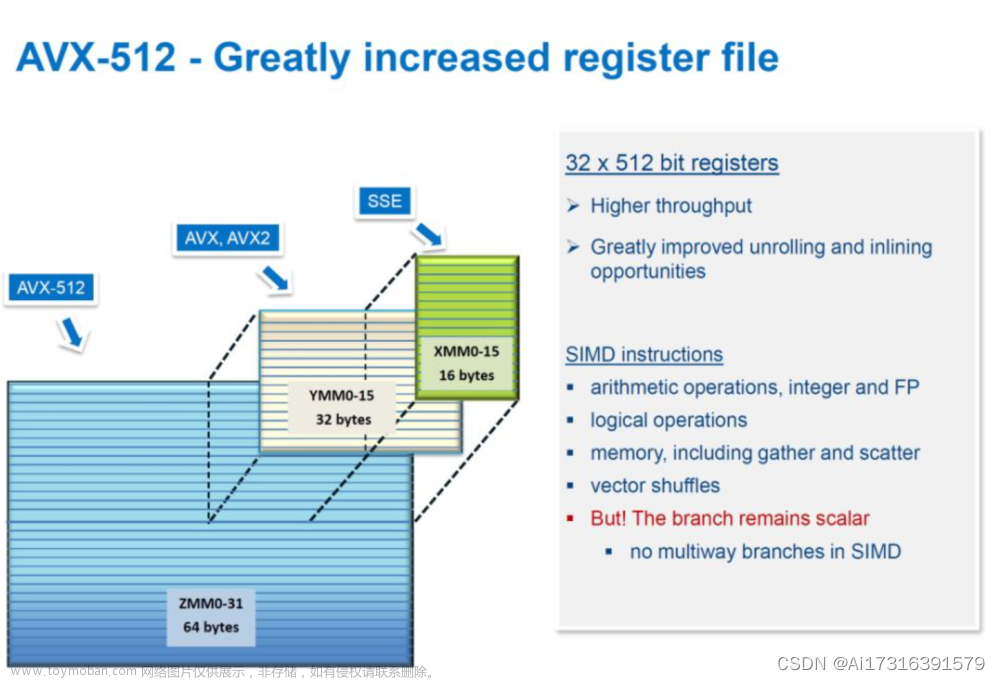

RAM又分两种, 一种是静态RAM,SRAM;一种是动态RAM,DRAM。前者的存储速度要比后者快得多,我们现在使用的内存一般都是动态RAM。 缓存通常都是静态RAM,速度是非常的快, 但是静态RAM集成度低(存储相同的数据,静态RAM的体积是动态RAM的6倍), 价格高(同容量的静态RAM是动态RAM的四倍), 但是为了提高系统的性能和速度,我们必须要扩大缓存, 这样就有了一个折中的方法,不扩大原来的静态RAM缓存,而是增加一些高速动态RAM做为缓存, 这些高速动态RAM速度要比常规动态RAM快,但比原来的静态RAM缓存慢, 我们把原来的静态ram缓存叫一级缓存,而把后来增加的动态RAM叫二级缓存。

一级缓存和二级缓存中的内容都是内存中访问频率高的数据的复制品(映射),它们的存在都是为了减少高速CPU对慢速内存的访问。

通常CPU找数据或指令的顺序是:先到一级缓存中找,找不到再到二级缓存中找,如果还找不到就只有到内存中找了。随着单个CPU中核数的增加,未来甚至可能会出现更多层级的缓存。

当CPU需要读取数据时,首先会检查缓存中是否有所需的数据。如果数据位于缓存中(命中缓存),CPU可以立即访问它,这样可以极大地提高数据的读取速度。如果数据不在缓存中(未命中缓存),CPU必须从内存中读取数据,这会导致较长的延迟。

缓存的存在使得CPU能够更有效地利用内存的数据,并减少对内存的频繁访问。较大的缓存可以容纳更多的数据,提高命中率,从而进一步提高计算机的性能。

总结起来,CPU、内存和缓存之间的关系可以概括为:CPU是计算机的处理器,内存是用于存储数据的设备,缓存则是位于CPU和内存之间的高速存储器,用于提高数据的读取速度。它们共同协作,以提供高效的计算机性能。文章来源:https://www.toymoban.com/news/detail-502345.html

文章来源地址https://www.toymoban.com/news/detail-502345.html

到了这里,关于计算机中CPU、内存、缓存的关系的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!