逻辑电路分为2大类,一类是组合逻辑电路,一类是时序逻辑电路

组合逻辑电路的特点:电路中任一时刻的稳态输出仅仅取决于该时刻的输入,而与电路原来的状态无关。组合电路没有记忆功能,只有从输入到输出的通路,没有从输出到输入的通路。

一,组合逻辑电路的分析

所谓分析,就是找出逻辑电路输出与输入之间的逻辑关系。

分析过程一般以以下步骤进行·

1,根据给定的逻辑电路,从输入端开始,逐级推导出输出端的逻辑函数表达式。

2,根据逻辑函数表达式列出真值表;

3,用文字描述逻辑函数实现的功能;

二,组合逻辑电路的设计

组合逻辑电路的设计是分析的逆过程,根据指定的逻辑功能,设计出实现这些功能的最佳逻辑电路

在设计中我们主要考虑一下几方面的我问题:

1,所用逻辑器件数目i少,器件种类少,且器件间连线简单(最小化电路)

2,满足速度要求,级数尽量少,以减少门电路的延迟

3,功耗小,工作稳定;

组合逻辑电路设计步骤:

1,逻辑抽象。即将文字描述转化为真值表。首先分析逻辑命题,确定输入,输出变量,然后用0,1两种状态分别对输入,输出变量进行逻辑赋值。最后根据输入,输出之间的逻辑关系列出真值表。

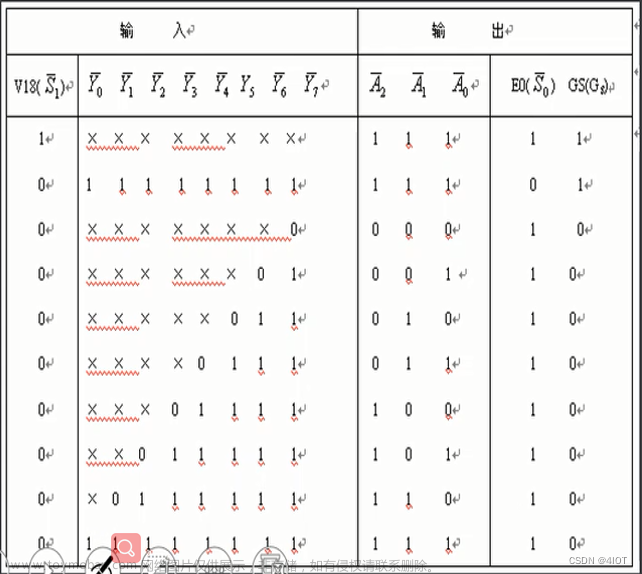

2.选择器件类型;根据命题要求,器件功能选择器件。对于多输入函数来说,常采用译码器实现电路比较方便,对于单输入函数来说采用数据选择器实现电路比较方便。

3,根据真值表和选用逻辑器件的类型,写出相应逻辑函数表达式。文章来源:https://www.toymoban.com/news/detail-513521.html

4,根据逻辑函数表达式和选用逻辑器件画出逻辑电路图。文章来源地址https://www.toymoban.com/news/detail-513521.html

到了这里,关于组合逻辑电路的分析与设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!