前言

-

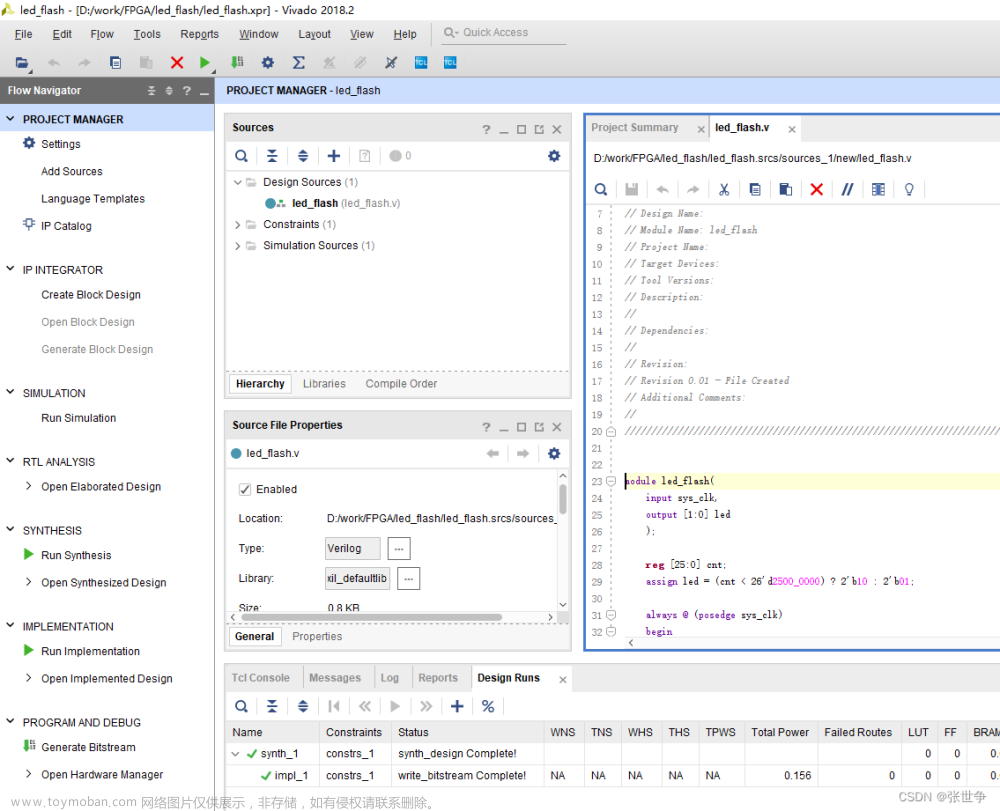

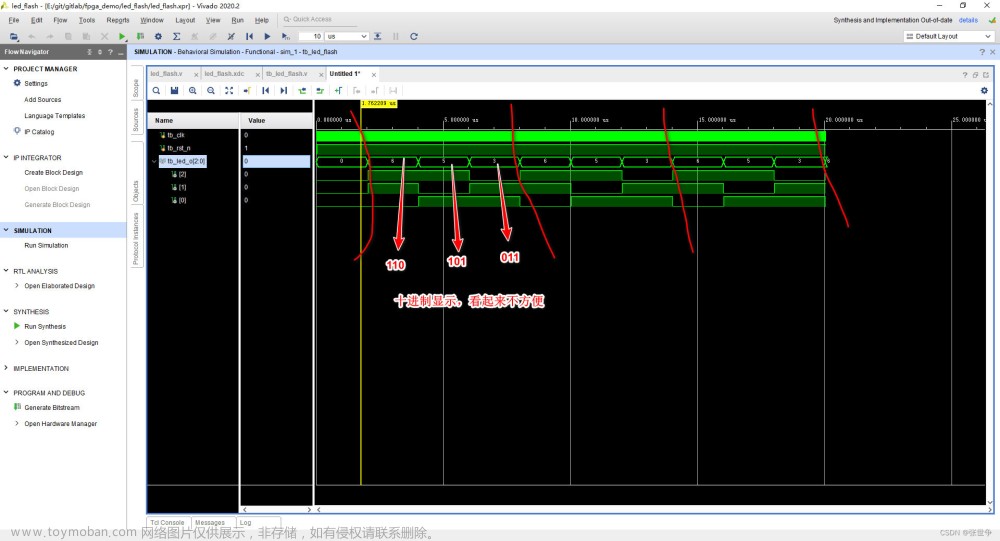

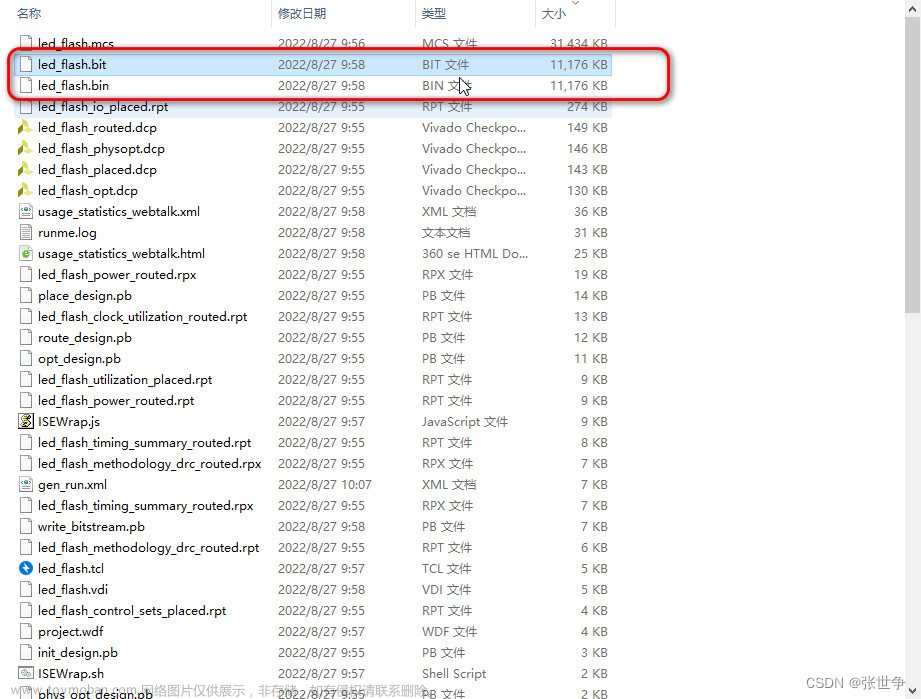

最近学习FPGA,使用Vivado,照着开发板例程,写了个流水灯的Verilog程序,配置好引脚约束后,下载到开发板,发现下载的速度有点慢,我一查看 生成的 bit文件,发现竟然接近11MB。

-

开始以为是 Vivado 版本出了问题,我先后更换为 Vivado 2018.2 Vivado 2019.2 Vivado 2022.2,生成的 bit 文件,竟然惊奇的一致。文章来源:https://www.toymoban.com/news/detail-535943.html

文章来源地址https://www.toymoban.com/news/detail-535943.html

文章来源地址https://www.toymoban.com/news/detail-535943.html

- 开启查看写的代码,发现只写了简单的几句,依旧是 接近 11MB,这样生成的 bin文件,固化到 SPI Flash,会相当的慢

bit 文件瘦身

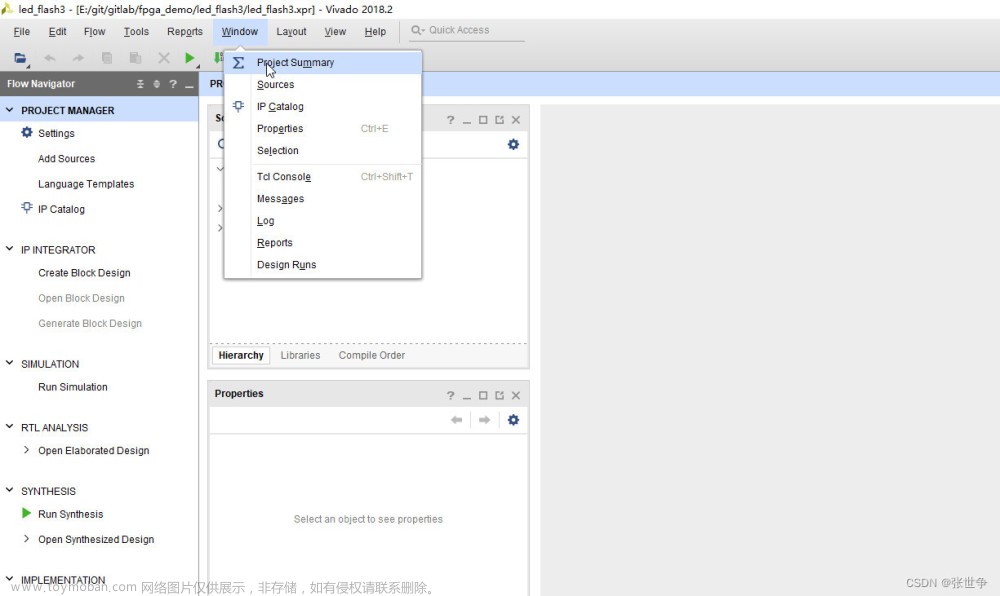

- 因为之前的一个工程,生成的 bin 文件比较的小,并且代码量很大,所以我对比了一下工程,发现约束文件里,一个配置项没有开启,我开启后,发现生成的代码变小为之前的 1/10左右,也就是不到1MB了

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VC到了这里,关于FPGA 学习笔记:Vivado 生成的 Bitstream bit 文件 超大的解决方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Vivado Error问题之[DRC NSTD-1][DRC UCIO-1] FPGA管脚约束问题导致生成bit时报错,如何在不重新Implentation情况下生成bit?](https://imgs.yssmx.com/Uploads/2024/01/804972-1.png)