目录

引言

关于使用112G Serdes的100G、200G和400G以太网的简要背景

自动协商的基础知识

基础页和下一页 / Base Page and Next Pages

DME基础页(IEEE802.3第73条)

下一页 (IEEE802.3)

下一页(以太网技术联盟)

AN过程

优先表决

链路训练

训练帧

链路训练过程

如何使用AN和LT

结论

Freya - Xena的112Gbps Serdes测试解决方案

FreyaCompact AN/LT测试设备

引言

对带宽需求的不断增加导致了服务提供商和数据中心向具有400Gbps、800Gbps甚至1.6Tbps以太网接口的25.6Tbps交换机架构发展。数据中心面临的一些关键挑战是连接器的密度、功耗和成本的均衡。

为了实现更高的端口速度,有一种趋势是每个通道LANE速度越来越高。目前的最高速度是106.25Gbps,使用四级脉冲振幅调制(PAM-4),即112GB/S PAM4,如IEEE 802.3ck规范中定义的那样。

传统上,高速以太网是通过光纤传输的,但这种解决方案既耗电又昂贵,消耗功率和成本都是很大挑战,主要表现在光电信号的效能转换,中间器件对电能的消耗等,尤其是光学传输的脆弱性对现场施工成本的增加等。对于只有几米长的机架间和机架顶部的短距离连接来说,DAC/AEC/ACC电缆会是一个更加选项。电线相比光纤的好处是,它可以实现更低成本和更低能耗。缺陷是在电缆上以106.25Gbps的速度传输PAM-4信号,会导致信号在频率相关损失、符号内干扰和通道串扰方面的问题[frequency dependent loss, inter-symbol-interference, and cross talk]。由于这个原因,均衡和前向纠错(FEC)是必须的,以保持足够低的误码率(BER),控制住链路的信号余量。

自动协商(AN,Auto-negotiation)和链路训练(LT,Link Training)是通过电缆连接进行以太网传输的关键因素,可以减少整体配置时间,将配置错误的风险降到最低,并优化性能。在自动协商过程中,两个互联的设备将交换有关其传输速度和FEC能力的信息,并就一组共同匹配的传输参数达成一致。然后,LT被用来自动调整每个设备的发射均衡器设置,以便在选定的传输速度下实现最小误码率。

在本白皮书中,我们将为基于112G SerDes的100Gbps、200Gbps和400Gbps以太网提供一个AN和LT的教程,以及需要AN和LT时的指南。[继续翻译一篇白皮书]

关于使用112G Serdes的100G、200G和400G以太网的简要背景

基于112Gbps的SerDes速度的100Gbps、200Gbps和400Gbps的以太网传输正在IEEE 802.3ck中得到标准化。

用于以太网的常见调制格式是 "非归零"(NRZ),其中每个符号周期携带一个比特的信息--即 "1 "或 "0"。然而,在IEEE802.3ck中,调制格式是4级脉冲振幅调制(PAM4),每个符号包含一个双比特值--即 "00"、"01"、"10 "或 "11"。符号率为53.125GBaud,导致单一PMD通道的数据率为106.25Gbps。用于106.25Gbps以太网的串行器-解串器(SerDes)被设计为112Gbps传输,以支持ITU-T建议的G.709光传输网络(OTN)标准,因此,SerDes被称为112G,尽管以太网的实际速度是106.25Gbps。

当信号被传输时,它们会损耗失真,最终导致接收端的比特错误。在112Gbps的SerDes速率和10-12的误码率(BER)下,每10秒就会发生一个误码。由于这个原因,在IEEE802.3ck标准工作中,100Gbps的BER要求被提高到10-14。

为了获得这些低水平的误码率,RS-FEC前向纠错是必须的MUST。前向纠错是一种编码技术,用于检测和纠正比特流中的错误,在发射器处增加冗余位形成纠错码。在接收端,FEC解码器使用这些额外的位来检测错误的位并纠正它们。在IEEE802.3ck中,FEC被定义为两个符号交错的Reed-Solomon(RS)(5440,5140,t=15),被称为100GBASE-R RS-FEC-Int,其中符号长度为10比特。

另一种改善信号完整性的方法是在发射器和接收器上都加入均衡器。由于本白皮书的内容是链路训练,而LT只影响发射器的均衡器,所以我们在此只考虑这个问题。

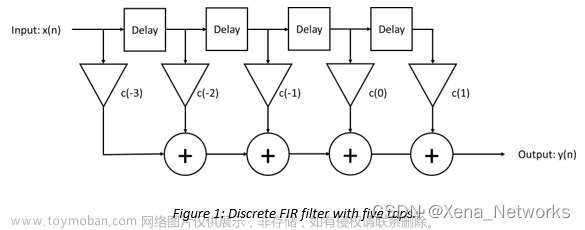

发射器均衡器是一个前馈均衡器(FFE),作为有限脉冲响应(FIR)滤波器实现。图1显示了IEEE802.3ck中为112Gbps SerDes定义的FIR滤波器。可以看出,FIR滤波器有5个抽头,这是从标准的早期版本中延伸出来的,后者定义的抽头较少。

输入的数字数据通过一系列的延迟线传播。每个延迟等于一个符号单位的时间间隔。滤波器的输出是当前符号(c(0))、前一个符号(c(+1))和后面三个符号(c(-1)、c(-2)和c(-3))的加权和。这个方案使均衡器能够调整由符号间干扰引起的误差。

自动协商的基础知识

自动协商Auto-Negotiate(ANEG或有时简写为AN)的主要目的是让链路端点的两个连接设备一起通信,并商定一套共同的传输参数。

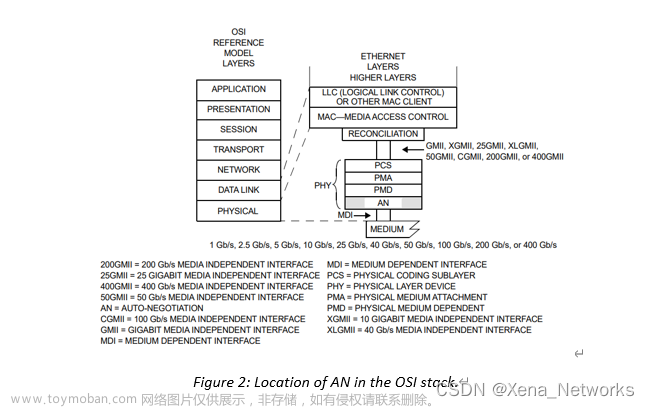

AN由OSI模型的物理层(PHY)处理,如图2所示。当然,首先要检查的是,两个端点是否启用了AN。如果其中一个端点不支持AN,这个过程自然会失败。

最初,AN过程在IEEE 802.3第28条中被标准化,并要求两个设备就一组预定义的能力进行协商,包括传输速度(技术能力)、双工模式(双工能力)和流量控制(暂停能力)。在第28条中,AN只被定义为10或100 Mbps BASE-T的双绞线,后来扩展到1、2.5、5和10 Gbps BASE-T。随着双轴电缆(-CR)和背板(-KR)上的更高速以太网的信令格式的改变,更多的速度选择,多线传输和前向纠错,AN标准已经被扩展,现在在IEEE 802.3条款73中描述。

AN协议使用链路码字(LCWs)进行通信。当两个设备通过电缆或背板连接时,它们会交换LCWs,以协商并同意一套共同的传输参数。对于太比特以太网来说,这通常会减少到速度和可能的FEC能力。

基础页和下一页 / Base Page and Next Pages

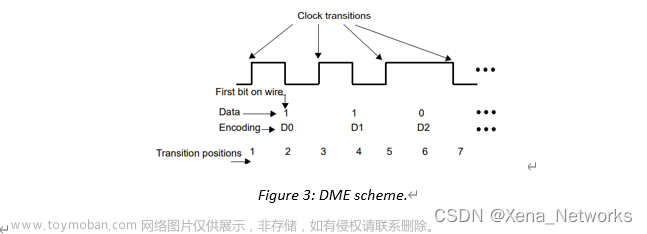

第28条和第73条的主要区别是,调制方案和速度已改为差分曼彻斯特编码(DME),LCW信息已扩展到48比特。LCW通常被称为基础页和下一页(或DME页)。随着新的速度和FEC选项被添加到标准中,第73条必须根据这些新技术能力进行更新但基础协议保持不变。

AN过程以156.25Mbps的比特率进行通信。由于这显然比电缆设计的实际速度低得多(每条通道可以达到100Gbps),DME信号将以高质量和无错误的方式传输。

对于多通道的连接,AN只在通道lane0上进行,其余的通道在AN期间禁用其SerDes。

图3说明了DME方案。信号中的每个奇数转换都用于时钟恢复,偶数转换编码DME页面的实际数据位。一个过渡编码为 "1",没有过渡则编码为 "0"。

DME基础页(IEEE802.3第73条)

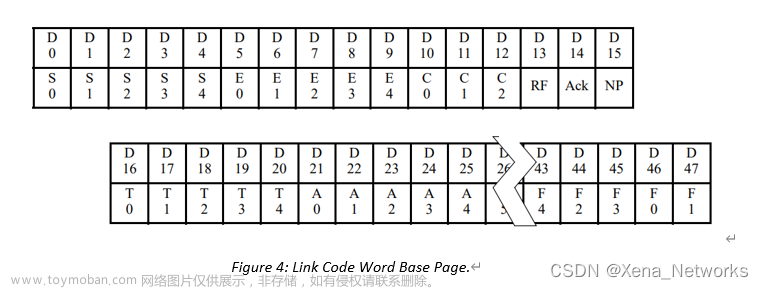

DME基础页的48位在IEEE 802.3标准的第73条中定义(见图4)

前五位是选择字段,决定使用哪个具体的IEEE标准。00001的二进制值表示DME页面符合IEEE 802.3标准。D21到D47位是表1中规定的速度和FEC技术能力字段,其编码方式是1表示支持给定的能力,0表示不支持。

| Bit |

Technology |

| A0 |

1000BASE-KX |

| A1 |

10GBASE-KX4 |

| A2 |

10GBASE-KR |

| A3 |

40GBASE-KR4 |

| A4 |

40GBASE-CR4 |

| A5 |

100GBASE-CR10 |

| A6 |

100GBASE-KP4 |

| Á7 |

100GBASE-KR4 |

| A8 |

100GBASE-CR4 |

| A9 |

25GBASE-KR-S or 25GBASE-CR-S |

| A10 |

25GBASE-KR or 25GBASE-CR |

| A11 |

2_5GBASE-KX |

| A12 |

5GBASE-KR |

| A13 |

50GBASE-KR or 50GBASE-CR |

| A14 |

100GBASE-KR2 or 100GBASE-CR2 |

| A15 |

200GBASE-KR4 or 200GBASE-CR4 |

| A16 |

100GBASE-KR or 100GBASE-CR |

| A17 |

200GBASE-KR2 or 200GBASE-CR2 |

| A18 |

400GBASE-KR4 or 400GBASE-CR4 |

| A19 – A21 |

Reserved for future technology |

| F4 |

100GBASE-P RS-FEC-Int Requested |

| F2 |

25G RS-FEC Requested |

| F3 |

25G BASE-R FEC Requested |

| F0 |

10 Gb/s per lane FEC Ability |

| F1 |

10 Gb/s per lane FEC Requested |

Table 1: Technology ability field encoding.

D5到D9和D16到D20位是回声和传输的Nonce(数字只使用一次)字段。这些字段可用于两个端点之间的认证,但具体用法没有被标准定义。暂停能力由D10到D12位发出信号。

远程故障(RF)位D13和确认(Ack)位D14被链路伙伴用来在AN过程中沟通状态。

下一页 (IEEE802.3)

对于IEEE802.3第73条自动协商,通常只需要交换图2所示的基本页。然而,该标准还定义了一个选项,以交换所谓的下一页。由于基础页只剩下三个未使用的技术位(A19-A21),IEEE正在努力定义下一页的特定位,以便在未来的标准中增加更多速度选项。

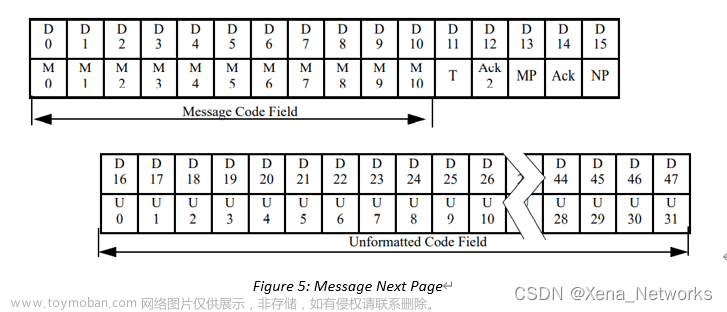

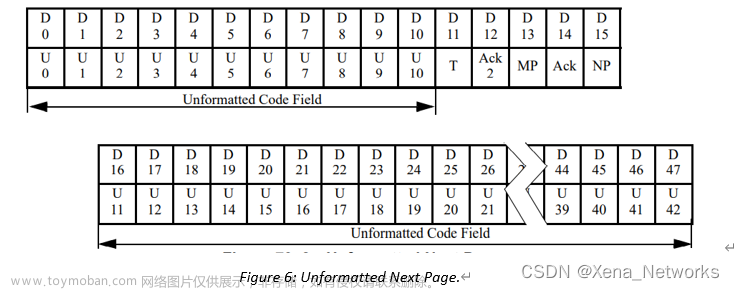

如果一个链路伙伴有一个下一页(NP)要传输,它将把NP位D15设置为1。下一页可以是信息下一页或未格式化的下一页,分别在图5和图6中定义。

如果两个链接伙伴的NP位都设置为1,他们可以交换下一页。如果一个链路伙伴没有下一页要发送,而它的链路伙伴有下一页要发送,它将发送带有Null消息代码的下一页,并且NP位设置为0,而它的链路伙伴发送有效的下一页。

下一页(以太网技术联盟)

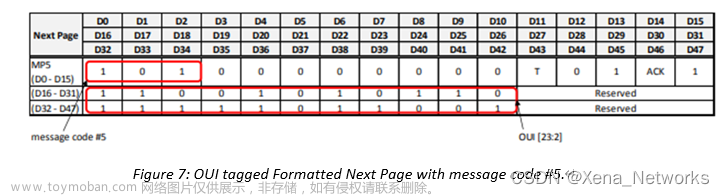

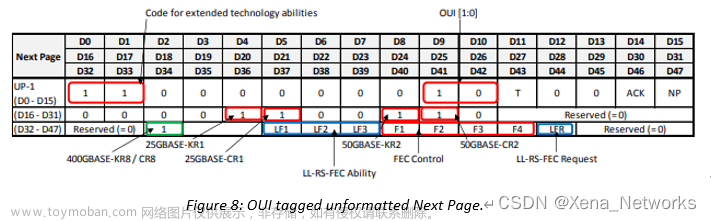

以太网技术联盟(ETC)已经定义了对IEE802.3协议的专有扩展。在链路伙伴交换了NP设置为1的基础页后,它们交换了一个组织唯一标识符(OUI)标记格式的下一页,信息字段设置为5(二进制101),如图7所示。

之后,链路伙伴交换一个带有扩展技术能力字段的OUI标记的未格式化的下一页,如图8所详述。这使设备能够发出信号,表明它们支持400GBASE-KR8/CR8和LL-RS-FEC(低延迟RS-FEC)等技术能力,而IEEE802.3没有定义这种能力。

AN过程

在AN过程中,每个链接伙伴持续发送相同的DME页面,直到远程链接伙伴确认正确收到DME页面。如果至少有一个链路伙伴有下一页,他们以同样的方式交换这些下一页,直到没有更多的下一页可以发送。

作为AN过程的一部分,定义了一些超时,以避免两个链接伙伴无休止地发送DME页面。

优先表决

一旦一个设备意识到它的链接伙伴的能力,它必须决定建立什么类型的链接。为了确保所有设备将选择相同的最高共同能力,它们必须实现优先级解决功能。这个功能只是对可能的技术进行排序,并要求设备选择支持的最高技术。表2显示了一个优先级决议表的例子。

每个链路伙伴执行一个仲裁过程,据此对本地端远程技术能力进行比较。如果双方都支持最高优先级的技术,则AN过程可以完成,链接可以建立。如果两个链路伙伴都不支持最高优先级,他们就会在优先级表(表2)中每次下移一步,直到达到他们都支持的技术能力。

文章来源地址https://www.toymoban.com/news/detail-594956.html

| Priority |

Technology |

Capability |

Note |

| 1 |

400GBASE-CR4 / KR4 |

400 Gbps 4 lanes |

IEEE mode |

| 2 |

400GBASE-CR8 / KR8 |

400 Gbps 8 lanes |

Ethernet Consortium mode |

| 3 |

200GBASE-CR2 / KR2 |

200 Gbps 2 lanes |

IEEE mode |

| 4 |

200GBASE-CR4 / KR4 |

200 Gbps 4 lanes |

IEEE mode |

| 5 |

100GBASE-CR or 100GBASE-KR |

100 Gbps 1 lane |

IEEE mode |

| 6 |

100GBASE-CR2 or 100GBASE-KR2 |

100 Gbps 2 lanes |

IEEE mode |

| 7 |

100GBASE-CR4 |

100 Gbps 4 lanes |

IEEE mode |

| 8 |

100GBASE-KR4 |

100 Gbps 4 lanes |

IEEE mode |

| 9 |

100GBASE-KP4 |

100 Gbps 4 lanes |

IEEE mode |

| 10 |

100GBASE-CR10 |

100 Gbps 10 lanes |

IEEE mode |

Table 2: Priority Resolution Table for 100, 200 and 400 Gbps Ethernet.

链路训练

当高数据率通过电缆传输时,接收到的数据流会严重失真,需要在恢复和正确采样之前进行均衡。均衡工作在发射器和接收器两端进行。

链路训练(LT)是一个最初在IEEE802.3第72条中定义的过程,用于10Gbps以太网的电缆,其中两个端点一起通信,以调整各自的发射器均衡器的设置,以达到最佳传输效果。每个接收器中的均衡器完全由接收器控制,不是LT过程的一部分。LT位于PHY的PMD内(见图2),也被称为PMD控制功能。

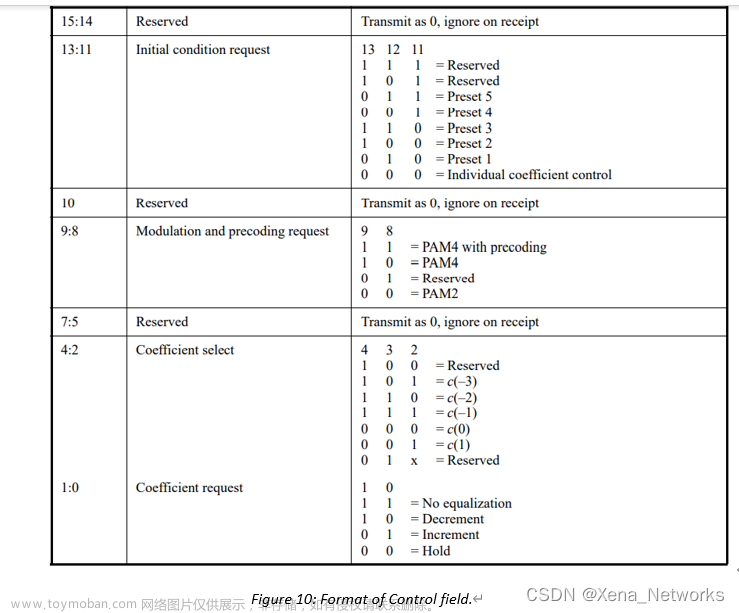

在LT过程中,调整的是图1上每个链路伙伴的发射器均衡器的系数c(-3)、c(-2)、c(-1)、c(0)和c(1)的权重。

与AN相比,LT协议在物理电缆上以实际速度运行。而且,随着速度的增加,FIR滤波器一般会得到越来越多的抽头。这意味着,每次引入新的速度和/或调制格式时,LT协议都必须进行调整。IEEE802.3第162条对112Gbps SerDes的100、200和400Gbps以太网的LT进行了描述。

训练帧

链路伙伴在LT期间使用训练帧进行通信。一个训练帧由控制信息和训练数据组成。控制词交换有关均衡器设置的信息,训练模式用于测试给定均衡器设置的性能。

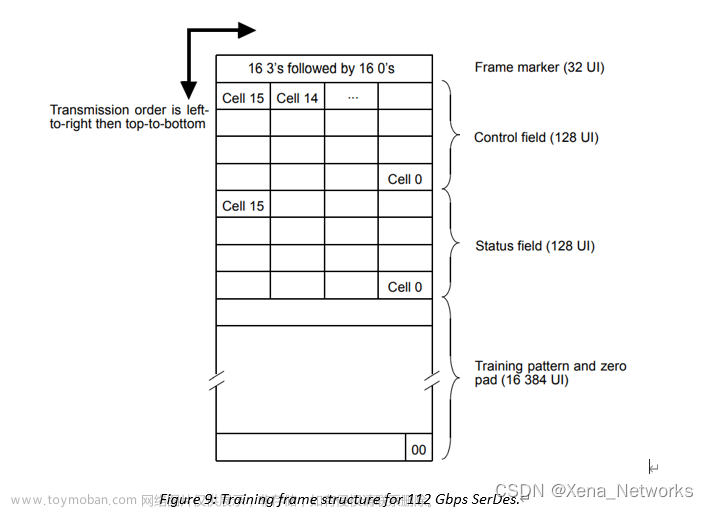

如图9所示,一个训练帧包括一个帧标记、一个控制字段、一个状态字段和一个训练模式字段。训练帧在所有PMD通道上独立发送。

帧标记、控制字段和状态字段都采用NRZ调制方式发送,高电平为PAM-4"3",低电平等于PAM-4"0"。帧标记由16个连续的PAM-4"3 "符号和16个连续的PAM-4"0 "符号组成,使接收器能够识别链路训练信号的开始。

控制字段和数据字段使用前面描述的差分曼彻斯特编码发送,高电平为PAM-4"3",低电平等于PAM-4"0"。控制字段和状态字段的传输速度是每个PMD通道全PAM-4符号率的1/8,即6.64Gbps。

训练模式是一个伪随机二进制序列(PRBS),以全PAM-4速度发送。该标准规定,训练以NRZ开始(即PAM-4"3 "和PAM-4"0"),以灰度编码的PAM-4或灰度编码和预编码的PAM-4结束。

LT的结束模式(有无预编码的PAM-4)也是LT完成后实际流量将使用的模式。

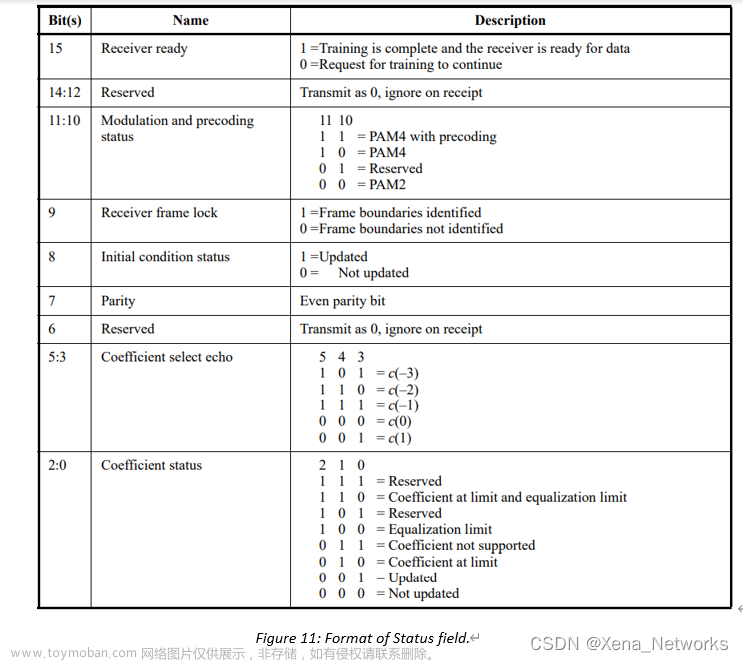

图10和图11分别指定了系数更新和系数状态字段的细节。

链路训练过程

在链路训练期间,每个链路伙伴将向其他链路伙伴发送建议,以通过系数更新域调整其在发射均衡器中的系数。这可能是一个耗时的过程,因为每个系数都必须单独调整,而且每发送一个训练帧,系数只能步进一个单位。

从PRBS训练模式得出的误码率可以用来测试每个训练帧的信号质量。

如何使用AN和LT

在安装高速以太网线卡时,可以说两个端点的传输速度已知是相同的,因此至少不需要AN。在本节中,我们将提供一些准则,说明何时需要AN和/或LT,何时不需要。

首先要考虑的是线卡是否由同一个OEM供应商提供。如果线卡来自不同的供应商,那么测试互操作性是必要的。测试第一层传输的AN和LT是一个很好的开始,以检查基本信号质量是否足够好。即使线路卡由同一供应商提供,而且互操作性或多或少得到保证,AN和LT仍有利于确保最佳性能。

不同的供应商可能以不同的方式实施均衡方案。例如,一些实施方案可能能够自动检测特定类型的电线,并相应地将发射均衡器调整为预设配置。然而,真正的性能只能从远端接收的信号中确定。因此,可以用LT来告诉发射机,预设均衡器设置是否良好或需要调整。

其次,你应该考虑是否所有的卡都能固定在同一速度,比如400GBASE-CR4。如果它们可以,在初始安装时仍应启用AN,因为你可能做了一些错误的配置。如果所有线卡都支持,LT将有助于调整PHY的均衡器。一旦系统投入使用,你可以禁用AN,但保持LT的启用,以捕捉由于电缆交换或其他外部影响造成的传输参数的变化。

结论

随着数据中心对高速、短距离连接的电缆越来越重视,基本的第一层信号完整性变得非常关键。此外,越来越多的速度、调制格式、前向纠错和车道数的组合正在被标准化。

因此,像自动协商(AN)和链路训练(LT)这样的基本以太网功能的重要性继续增加。自动协商有助于确定两个链路伙伴所支持的最高共同技术能力(通常是速度),而链路训练则有助于两个链路伙伴调整其传输均衡器,以实现最低的误码率。

Freya - Xena的112Gbps Serdes测试解决方案

Xena的Valkyrie TGA平台现在包括Freya,这是一系列测试模块,具有在第1层、第2层和第3层测试高速112Gbps SerDes以太网设备和链接所需的功能。

对于第1层,测试基于112Gbps SerDes系统的相关信号完整性参数包括自动协商、链路训练(用于电缆)、高级PHY均衡器调整、PRBS测试、预FEC错误分布和信号完整性视图。

有关Xena的Freya测试模块的信息,见:https://xenanetworks.com/freya-ethernet-testing-for-pam4-112gbps-serdes-for-100g-200g-400g-800g/

FreyaCompact AN/LT测试设备

正如本白皮书明确指出的那样,自动协商和链路训练(AN/LT)是通过电缆进行高速、短距离连接的关键以太网功能,因为它们有助于在发送真正的L2/L3流量之前在两个设备之间建立链接。

为了帮助公司测试和调试基于56/112Gbps SerDes的以太网的AN/LT协议,信雅纳厂商提供了一个独立的产品,称为FreyaCompact AN/LT测试设备。

与Xena的其他Freya测试模块不同,FreyaCompact AN/LT测试设备不包括流量生成和分析(TGA)功能。

相反,FreyaCompact AN/LT测试设备可以让开发人员一次完成一个信息的协议,使他们能够快速、轻松地识别实施中可能的错误或时间问题。

FreyaCompact AN/LT测试设备还可以通过禁用测试设备中的自动均衡器适应来测试远程设备的真实均衡器性能。

这些功能可通过两个SW应用程序(与硬件一起提供)实现,这些应用程序基于Xena OpenAutomation(XOA),Xena新的开源脚本和测试自动化平台。

1. AN/LT协议测试工具是一个交互式的命令行界面,使AN/LT协议开发团队能够轻松地单步完成AN/LT的配置。

2. 2.AN/LT协议测试套件是针对那些想对AN/LT进行性能和合规性测试的实验室,因此需要可配置的测试脚本和测试报告。

FreyaCompact AN/LT测试设备有两个硬件版本,一个用于QSFP-DD800,另一个用于OSFP。

相关白皮书

1. ''Terabit Ethernet - Why?

2. "Terabit太比特以太网--How?"

3. 使用112Gbps SerDes测试400GE

或预约信雅纳(Xena Networks)的技术专家。文章来源:https://www.toymoban.com/news/detail-594956.html

到了这里,关于聚焦112Gb/s SerDes芯片的AN/LT端口自协商和链路学习,评估验证高速链路的信号质量并分析调优(400/800G高速以太网互联接口,AI加速卡网络RDMA性能测试,交换背板接口性能评估)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!