@

-

一、TCL语言和synopsys TCL语言入门

- 1.1 TCL基本指令

- 1.2 synopsys TCL常用语言

-

二、STA基本概念

- 2.1 时序弧(Timing Arc)与线延迟、单元延迟

- 2.2 建立时间与保持时间

- 2.3 时序路径(Timing path)

- 2.4时钟域(Clock Domains)

- 2.5 操作条件(Operating Conditions)和 PVT(Process Voltage Temperature)

-

三、标准单元工艺库

- 3.1 库文件概述

- 3.2 非线性延迟模型

- 3.3 电平翻转阈值调整(slew_derate)

-

四、建立静态时序分析的环境

-

4.1 Specifying Clocks

- 4.1.1(主)时钟定义

- 4.1.2.时钟不确定度(set_clock_uncertainty)

- 4.1.3 时钟延迟

- 4.2 Generated Clocks

- 4.3 Constraining Input Paths and Output Path

- 4.4 Design Rule Checks(DRC)

- 4.5 Virtual Clocks

- 4.6 Refining the Timing Analysis

-

4.1 Specifying Clocks

-

五、时序检查

-

5.1 建立时间与保持时间检查方法

- 5.1.1建立时间检查

- 5.1.2保持时间检查

-

5.2 多周期路径、半周期路径、伪路径时序检查

- 5.2.1 多周期路径检查

- 5.2.2 半周期路径

- 5.2.3 伪路径

- 5.3 恢复时间与去除时间

-

5.4 跨时钟域时序

- 5.4.1 慢时钟域到快时钟域

- 5.4 2 快时钟域到慢时钟域

-

5.5 多时钟

- 5.4.1 整数倍关系

- 5.4.2 非整数倍关系

- 5.4.3 相移关系

-

5.1 建立时间与保持时间检查方法

-

六、鲁棒性检查

-

6.1 片上变化(OCV)

- 6.1.1 降额(derate)

- 6.1.2 CPPR

- 6.1.3 在最严苛的工艺下的建立时间与保持时间时序检查

- 6.2 时间借用(Time Borrowing)

- 6.3 数据到数据检查

- 6.4 门控时钟检查

-

6.1 片上变化(OCV)

- 参考资料

一、TCL语言和synopsys TCL语言入门

基本目标:

1.掌握常用TCL基本指令(至少要看得懂)

2.掌握常用synopsys TCL常用指令,包括信息与属性的获取以及过滤

3.重点关注TCL正则匹配与文本处理方法,能够写出简单的文本处理脚本

1.1 TCL基本指令

置换:变量置换$、命令置换[]、反斜杠置换\

变量赋值与输出:set、puts

其他:\t、\n、""、{}、#

set X 1.2

set Y 1.3

puts "[expr $X + $Y]"

#结果为2.5

puts "\[expr $X + $Y\]"

#结果为[expr 1.2 + 1.3]

puts "\[expr \$X + \$Y\]"

#结果为[expr $X + $Y\]

puts {\[expr \$X + \$Y\]}

#结果为[expr \$X + \$Y\]

数组:使用array指令获取数组信息

set cell_1(ref_name) "bufx2"

set cell_1(full_name) "top/cell_1"

set cel1_1(pins) "A B C"

puts $cell_1(ref_name)

#结果为bufx2

arry size cel1_1

#结果为3

arry names cel1_1

#结果为ref_name full_name pins

列表:concat、lindex、llength、lappend、lsort

set list1 {bufx1 bufx2 bufx4}

set list2 {ivtxl ivtx2 ivtx4}

concat $list1 $list2

#输出结果为bufx1 bufx2 bufx4 ivtxl ivtx2 ivtx4

llength $list1

#输出结果为3

llength [concat $list1 $list2]

#输出结果为6

lindex $list1 1

#输出结果为bufx2

lindex $list1 [expr [llength $list1] - 1]

#输出结果为bufx4

lappend list1 bufx5

#输出结果为bufx1 bufx2 bufx4 bufx5

set list3 {4 1 2 3 2 1}

lsort -real $list3

#按数字大小排序,输出结果为1 1 2 2 3 4

lsort -unique $list3

#按唯一性输出1 2 3 4

控制流:if、foreach、break、continue、while、for

Tips:脚本语句的'{'一定要写在上一行,因为如果不这样,TCL 解释器会认为if命令在换行符处已结束,下一行会被当成新的命令,从而导致错。

if

foreach……break

foreach……continue

while

for

过程函数:proc

Tips:指令global,可以在过程内部引用全部变量

proc proc_name {argument} {

......

return return_value

}

正则匹配:

\w,用来匹配一个字母、数字、下划线

\d ,用来匹配一个数字

\s表示空格

. 表示任意一个字符

正则匹配-量词

正则匹配-锚位

捕获变量

文本处理

1.2 synopsys TCL常用语言

1.信息获取

#语法

get_ports 端口名称

get_cells 单元名称

get_nets 网表名称

get_pins 管脚名称

获取信息的时候可以搭配通配符*去获取想要的信息,以get_ports指令为例子:

get_ports * #返回所有的端口名称

get_ports I* #返回所有的以I开头的端口名称

get_ports *1 #返回所有的以1结尾的端口名称

2.属性获取

get_attribute [get_cells 单元名] ref_name

#单元对象 的 ref_name 属性:用来保存其映射到参考单元的名称

get_attribute [get_nets 网表名] full_name

#网表对象 的 full_name 属性:用于保存网表名称

get_attribute [get_pins 单元/引脚] owner_net

#引脚对象 的 owner_net 属性:用来保存与之相连的网表名称

get_attribute [get_ports 单元名] direction

#端口对象 的 direction 属性:用来保存端口的方向

3.属性过滤和对象连接

get_ports 端口名 -f "过滤条件"

#“-f”可以用来过滤属性,以得到我们想要的object

get_nets -of [get_ports 端口名]

#“-of”可以用来得到指定object相连接的object

二、STA基本概念

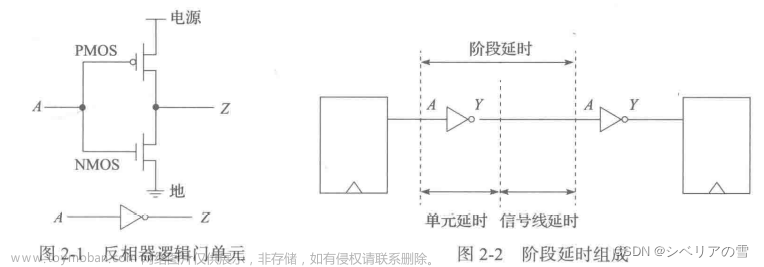

2.1 时序弧(Timing Arc)与线延迟、单元延迟

时序弧用来描述,两个节点延时信息的参数。通常分为Net delay(线延迟)和Cell delay(单元延迟)。其中Cell delay(单元延迟)内部有两种延迟,分别为 Transition delay(翻转延迟)和Logic gate delay(逻辑门延迟)。

2.2 建立时间与保持时间

建立时间:在触发器的捕获沿到来之前,数据必须提前保持稳定的持续时间,以保证触发器可以顺利安全的取到数据。此参数可以用来约束数据路径上的最大时序。

保持时间:在触发器的捕获沿到来之后数据必须保持稳定的持续时间。此参数可以用来约束数据路径的最小时序。

Tips:建立时间与保持时间对应的最大延时和最小延时不要记反了!

2.3 时序路径(Timing path)

PrimeTime 进行时序分析的第一步是将设计分解为一组时序路径。每个时序路径都有一个起点和终点,起点和终点各有两种,起点包括 clock pin 和 input port,终点包括data input pin 和 output port,所以一共有四种时序路径。

2.4时钟域(Clock Domains)

大多数数字电路都是“全局异步,局部同步”的时序,但是所有的静态时序分析(STA)都是针对的同步电路。

2.5 操作条件(Operating Conditions)和 PVT(Process Voltage Temperature)

由于半导体不同的工艺制成,不同的使用环境,对器件本身的延迟存在较大影响。所以在进行STA时一定要明确操作的环境和条件,主要包括工艺制程(Process)、电压(Voltage)、温度(Temperature)。在指定上述的条件之后,单元延时和互连线的延时也就根据上述条件进行计算分析。

工艺制程的模型主要分为3种:slow、typical、fast。其中 slow 和 fast都是极端的条件,对于稳健的设计,PVT(Process Voltage Temperature)都要在极端环境下测试通过。高温低压对应最坏的情况,低温高压对应最佳情况。

一般在最大延迟环境下检查建立时间,在最小延迟环境下检查保持时间。

三、标准单元工艺库

3.1 库文件概述

通过库文件可以读出单元的相关信息,如下图所示:

具体可以参考:静态时序分析(STA)—— 标准单元库

3.2 非线性延迟模型

单元延迟取决于两个因素:输出负载电容和电平转换时间

1、输出负载,即输出端的电容负载的大小。容性负载越大,延迟越大。

2、输入端信号高低电平转换时间。大多数情况下,此参数越大,对应的延时也会越大。

根据电容负载和电平转换时间可以推导出线性延迟模型去预估模型的具体延迟。然而,线性模型在微小工艺半导体器件中并不是很精确,大都数用的是非线性模型。

第一步:根据查表法得到对应的延时。

第二步:如果找不到对应的点,则根据相邻的四个点进行插值然后根据高斯消元法得到模型延时。

3.3 电平翻转阈值调整(slew_derate)

电平翻转阈值调整主要是应对一些实际工艺制程与工艺库的不同导致延迟差异的问题。例如工艺库单元阈值为10%—90%,而实际的工艺为30%—70%,阈值相当于下降了50%。为了解决这类问题,只需要slew_derate_from_library设置为0.5即可。如下图所示:

四、建立静态时序分析的环境

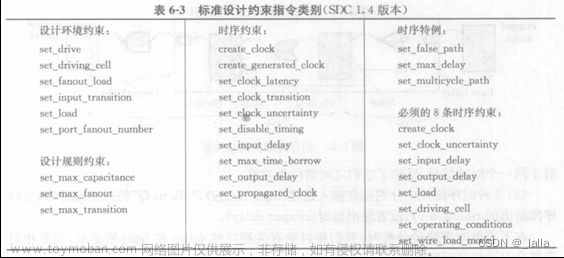

正确的约束对于分析STA结果很重要,只有准确指定设计环境,STA分析才能够识别出设计中的所有时序问题。STA的准备工作包括设置时钟、指定IO时序特性以及指定伪路径和多周期路径。

什么是STA环境?大部分数字设计是同步的,从前一个时钟周期计算出的数据在时钟有效沿上被锁存在触发器中。为了对这种设计执行STA,需要指定触发器的时钟、以及进入设计和退出设计的所有路径的时序约束。

4.1 Specifying Clocks

4.1.1(主)时钟定义

要定义时钟,我们需要提供以下信息:时钟源(Clock source)、周期(Period)、占空比(Duty cycle)边沿时间(Edge times)。

以下是一个基本的时钟约束规范:

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

4.1.2.时钟不确定度(set_clock_uncertainty)

可以使用set_clock_uncertainty约束来指定时钟周期的时序不确定度(uncertainty),该不确定度可用于对可能会减少有效时钟周期的各种因素进行建模。 这些因素可能是时钟抖动(jitter)以及可能需要在时序分析中考虑的任何其它悲观度。建立时钟不确定性声明,会使整个电路的时序变得更加严苛,满足设计的稳健性。

时钟不确定性的主要来由:

时钟偏差(clock skew):时钟源到达不同触发器的时间偏差

时钟抖动(clock jitter):时钟边沿的超前或滞后

时钟延迟(clock delay):网络延迟和源延迟

对于保持时间检查,时钟不确定度将用作需要满足的额外时序裕量,如下图所示:

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

以下命令可用于指定跨时钟边界路径上的时钟不确定度:

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYSCLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYSCLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

4.1.3 时钟延迟

时钟延迟分为两种类型:网络延迟(network latency)和源延迟(source latency)。网络延迟是指从时钟定义点(create_clock)到触发器时钟引脚的延迟,源延迟是指从时钟源到时钟定义点(create_clock)的延迟。具体如下图所示:

以下指令可以指定时钟的延迟:

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

# Specify a network latency (no -source option) of 0.8ns for rise, fall, max and min.

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

# Specify a source latency

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

# Specify a min source latency

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

# Specifv a max source latency

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

# Specify a rise latency

set_clock_latency 2.1 -fall [all_clocks]

# Specify a fall latency

4.2 Generated Clocks

衍生时钟是从主时钟(master clock)派生而来的时钟,主时钟是指使用create_clock命令定义的时钟。在基于主时钟的设计中生成一个新时钟时,可以将这个新时钟定义为衍生时钟。

例如根据一个时钟周期为10的主时钟CLKP生成一个二分频衍生时钟CLKPDIV2,指令示例如下:

create_clock -name CLKP 10 [get_pins UPLL0/CLKOUT]

#主时钟

create_generated_clock -name CLKPDIV2 -source UPPL0/CLKOUT -divide_by 2 [get_pins UFF0/Q]

#衍生时钟

可以在触发器的输出端定义一个新的时钟,即主时钟,而不是生成的时钟吗?

答案是肯定的,但是有一些缺点。定义一个主时钟而不是一个衍生时钟会创建一个新的时钟域,软件工具会当做异步时钟处理而不是同步时钟处理。将新时钟定义为衍生时钟不会创建新的时钟域,并且衍生时钟被认为与其主时钟同相,衍生时钟不需要开发额外的约束。因此,尽量将内部新生成的时钟定义为衍生时钟,而不是将其声明为另一个主时钟。

主时钟和衍生时钟之间的另一个重要区别是时钟源的概念。在主时钟中,时钟源位于主时钟的定义点。而在衍生时钟中,时钟源是主时钟的源而不是衍生时钟的源。这意味着在时钟路径报告中,时钟路径的起点始终是主时钟的定义点。这样一来,与定义新的主时钟相比,衍生时钟具有很大优势,是不会自动考虑源延迟的。因此,由衍生时钟驱动的触发器的时钟引脚的总时钟延迟是主时钟源延迟、衍生时钟源延迟和衍生时钟网络延迟的总和。如下图所示:

相反的,如果时钟操作输出的时钟和源时钟没有太多关系(不是直接的倍频分频等),失去了相位和周期的继承性,那么此时输出的时钟就是可以定义为主时钟,而非衍生时钟。

4.3 Constraining Input Paths and Output Path

为什么需要进行输入输出路径的约束?

这里需要注意的一点是,STA无法检查不受约束的路径上的任何时序,因此需要约束所有路径以进行时序分析。输入输出路径的约束关系可以用来确定可靠地捕获DUA内部数据的可用时间。

1.输入路径约束

让我们同时考虑最大和最小延迟情况,以下是输入路径的约束:

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

可以通过约束关系得到:CLK到INPA的最大延迟为和最小延迟分别为6.7ns和3.0ns,已知时钟周期为15ns,则可以得到8.3ns是用来可靠地捕获DUA内部数据的可用时间。

2.输出路径约束

让我们同时考虑最大和最小延迟情况,以下是输入路径的约束:

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

可以通过约束关系得到:CLKQ到OUTC的最大延迟为和最小延迟分别为7.4ns和-0.2ns,已知时钟周期为15ns,则可以得到7.6ns是OUTC必须保持稳定状态的时间。

3.输入输出路径约束

补充:

1.了解时序路径组(Timing Path Groups):由终点决定命名

2.了解外部属性建模(Modeling of External Attributes

):对于输入,需要在输入端口处指定驱动强度;对于输出,需要指定输出引脚的负载电容;

#输入驱动

set_drive 100 UCLK

set_drive -rise 3 [all_inputs]

set_drive -fall 2 [all_inputs]

#指定驱动强度,数字代表驱动电阻,电阻越小驱动强度越高,0表示无限的驱动强度

#第一种已经过时,不推荐

set_driving_cell -lib_cell INV3 -library slow [get_ports INPB]

set_driving_cell -lib_cell INV2 -library tech13g [all_inputs]

set_driving_cell -lib_cell BUFFD4 -library tech90gwc [get_ports {testmode[3]}]

#指定驱动输入端口的单元类型

#第二种功能同第一种,用法更精准更方便

set_input_transition 0.85 [get_ports INPC]

set_input_transition 0.6 [all_inputs]

set_input_transition 0.25 [get_ports SD_DIN*]

#输入端口表示过渡时间的便捷方法

#第三种更为直接,直接指定输入端口的转换时间;

#输出驱动

set_load 5 [get_ports OUTX]

set_load 25 [all_outputs]

set_load -pin_load 0.007 [get_ports {shift_write[31]}]

#输出负载影响驱动输出的单元的延迟,数值越小延迟越小

4.4 Design Rule Checks(DRC)

STA中两个常用的设计规则是最大过渡时间-max_transition和最大电容-max_capacitance。这些规则将会检查设计中的所有端口和引脚是否满足过渡时间和电容的规定约束。作为STA的一部分,任何设计规则的违例(violation)均以裕量(slack)的形式报告。这些规则可以使用以下命令指定:

set_max_transition 0.6 IOBANK

set_max_capacitance 0.5 [current_design]

4.5 Virtual Clocks

虚拟时钟存在但是不和设计中的端口和引脚相连接。它在STA分析中用作参考,以指定相对于时钟的输入和输出延迟。

4.6 Refining the Timing Analysis

用于精细化约束分析的四个常用命令是:

set_case_analysis

#在单元的引脚或输入端口上指定常量值。

set_disable_timing

#中断单元的时序弧。

set_false_path

#指定实际不存在的路径,这意味着在STA中不需要检查这些路径。

set_multicycle_path

#指定可能花费超过一个时钟周期的路径。

1.指定无效信号

主要面临的情况是DFT、多功能模式和MUX:

1.如果芯片中具有DFT(可测性设计)逻辑,则在正常功能模式下,芯片的TEST引脚将一直为0。

2.如果设计具有多种功能模式,而只需要分析其中一种功能模式,则可以使用set_case_analysis来指定要分析的模式。

3.在MUX设计中指定set_case_analysis,分别对每个信号进行分析是十分必要的。

set_case_analysis 0 TEST

set_case_analysis 0 [get_ports {testmode[3]}]

set_case_analysis 0 [get_ports {testmode[2]}]

set_case_analysis 0 [get_ports {testmode[1]}]

set_case_analysis 0 [get_ports {testmode[0]}]

#指定DFT端信号无效

set_case_analysis 1 func_mode[0]

set_case_analysis 0 func_mode[1]

set_case_analysis 1 func_mode[2]

#具有多功能的模块,对每个功能分别单独分析

set_case_analysis 1 UCORE/UMUX0/CLK_SEL[0]

set_case_analysis 1 UCORE/UMUX1/CLK_SEL[1]

set_case_analysis 0 UCORE/UMUX2/CLK_SEL[2]

#对MUX每个信号单独分析

2.中断单元内的时序弧

在某些情况下,单元中的一条路径可能无法发生。由于时序弧不再存在,因此需要分析的时序路径更少。

使用set_disable_timing命令需要格外小心,因为它会删除通过指定引脚的所有时序路径。在可能的情况下,最好使用set_false_path和set_case_analysis命令。

set_disable_timing -from S -to Z [get_cells UMUX0]

#直接中断时序弧

3.伪路径时序分析

指定实际不存在的路径,这意味着在STA中不需要检查这些路径。伪路径约束很重要,对于跨时钟域的模块之间的路径,不予分析。注意,伪路径约束是单向的。伪时序路径后文重点分析。

4.多周期路径时序分析

信号传输可能花费超过一个时钟周期的路径。输入到输出的延迟跨越了多个时钟周期。多周期时序路径后文重点分析。

五、时序检查

5.1 建立时间与保持时间检查方法

5.1.1建立时间检查

建立时间检查可以用数学公式表示:

$$T_{launch}+T_{ck2q}+T_{dp} < T_{capture}+T_{cycle}-T_{setup}$$

通常,有一个发起触发器(用于发起数据的触发器)和捕获触发器(用于捕获数据的触发器),这个捕获触发器的建立时间要求必须满足上述公式。换而言之,数据到达捕获触发器D引脚所花费的总时间必须小于时钟传输到捕获触发器所花费的时间加上时钟周期再减去建立时间要求。

由于建立时间检查受到 -max的约束,因此建立时间检查始终使用 最长或最大的时序路径。出于同样的原因,通常在 延迟最大的慢工艺角(slow corner)下执行建立时间检查。

具体时序如下所示:

在前面我们知道时序路径有四种,如下为触发器到触发器的时序报告:

其他三条时序路径不再赘述,具体可查看静态时序分析圣经翻译计划——第八章:时序检查(上)

时序报告中的时钟网络延迟(clock network delay)是什么?为什么将其标记为理想(ideal)?

时序报告中的这一行表明时钟树被认为是理想的,时钟路径中的任何缓冲器(buffer)都假定为零延迟。一旦构建了时钟树,就可以将时钟网络标记为“已传播”(propagated),从而使得时钟路径显示实际延迟值,例如时序报告中所示:0.11ns延迟是发起时钟上的时钟网络延迟,而0.12ns延迟是捕获触发器上的时钟网络延迟。

5.1.2保持时间检查

保持时间时间检查可以用数学公式表示:

$$T_{launch} + T_{ck2q} + T_{dp} > T_{capture} + T_{hold}$$

保持时间是在发起触发器(发起数据的触发器)和捕获触发器(捕获数据的触发器以及必须满足其保持时间要求的触发器)之间进行检查的,保持时间检查从发起触发器时钟的一个有效沿到捕获触发器中相同的时钟沿。因此,保持时间检查与时钟周期无关,保持时间检查会在捕获触发器时钟的每个有效沿上执行。

保持时间检查对捕获触发器的数据路径施加了最小值 -min 约束,使用 最短或最小的时序路径来进行保持时间检查,同样,在 延迟最小的快工艺角(fast corner)下执行建立时间检查。

具体时序如下所示:

在前面我们知道时序路径有四种,如下为触发器到触发器的时序报告:

Tips:对于建立时间与保持时间的裕值slack的计算并不相同,建立时间的slack为数据需要到达时间 - 数据实际到达时间,正值则表示不违例;保持时间的slack为数据需要到达时间 - 数据实际到达时间,然后添加负号,最终正值则表示不违例。(时序报告数据实际到达时间的“-”表示此为时间为实际到达时间,计算时去绝对值即可)

5.2 多周期路径、半周期路径、伪路径时序检查

5.2.1 多周期路径检查

在某些情况下,两个触发器之间的数据路径可能需要一个以上的时钟周期才能传播通过逻辑。在这种情况下,这条组合逻辑路径会被定义为多周期路径(multicycle path)。虽然数据还是会在每个时钟沿上都被捕获触发器捕获,但我们需要告知STA在指定数量的时钟周期之后才会出现有效的捕获时钟沿。

对多周期路径进行如下约束:

create_clock -name CLKM -period 10 [get_ports CLKM]

#主时钟CLKM

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

#建立时间多周期约束

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

#保持时间多周期约束,将保持时间检查边沿前移两个时钟周期

Tips:如果保持时间的检查边沿没有移动到launch edge,则对于后序的保持时间要求太严苛,即数据在多周期都要求保持不变,这显然是难以实现的。只有对保持时间的检查边沿前移 N-1 个时钟周期才能更加满足时序要求。

建立时间时序报告

保持时间时序报告

5.2.2 半周期路径

如果设计中同时具有负边沿触发的触发器(有效时钟沿为下降沿)和正边沿触发的触发器(有效时钟沿为上升沿),则设计中可能存在半周期路径(half-cycle path)。半周期路径可能是从一个触发器的上升沿到另一个触发器的下降沿,或者反过来。半周期导致建立时间时序更加严苛,而保持时间时序更加宽松。

5.2.3 伪路径

当设计的功能运行时,某些时序路径可能不真实(或不可能)存在。在执行STA时可以将这些路径设置为伪路径(false path),这样就可以关闭这些路径,那么STA就不会对这些伪路径去进行分析了。一般来说,跨时钟域信号涉及的路径都不用STA,所以跨时钟域的路径都需要设置伪路径。

set_false_path -from [get_clocks clockA] -to [get_clocks clockB]

set_false_path -from [get_pins {regA_ * }/CK] -to [get_pins {regB_ * }/D]

set_false_path -through [get_pins UMUX0/S]

Tips:

①少用-through选项,因为会增加时序分析的复杂程度。仅在绝对有必要且没有替代方法可以指定该伪路径的情况下,才可以使用-through选项。

②尽量直接抓取时钟,例如第一条约束与第二条约束,速度更快。

③不要将一条多周期路径约束为伪路径。

5.3 恢复时间与去除时间

恢复时间(Recovery Time):是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,如果保证不了这个最小恢复时间,没有给寄存器留有足够时间来恢复至正常状态,那么由于离得太近就不能保证“下个时钟沿”能正常作用导致“时钟沿”可能会失效。

去除时间(Removal Time):是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,如果保证不了这个去除时间,那么由于离得太近就不能保证有效地屏蔽这个“时钟沿”。

尤其注意,恢复时间与去除时间是针对异步控制信号而言的!如果不对异步控制信号进行 Recovery Time 和 Removal Time 时序约束,也就是说可能会造成寄存器处于不确定的状态。而这些情况是应该避免的。

Tips:单从时序的位置看,可以将恢复时间、去除时间类比为建立时间、保持时间。

5.4 跨时钟域时序

5.4.1 慢时钟域到快时钟域

时序分析一般选择最严苛的路径进行分析,最严苛的建立时间和保持时间时序如下图所示:

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

#时钟定义

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

#多周期约束检查建立时间

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

##多周期约束检查保持时间

5.4 2 快时钟域到慢时钟域

时序分析一般选择最严苛的路径进行分析,最严苛的建立时间为 Setup4,如果对时序放宽松则选择其他检查边沿,例如以 Setup2 作为检查边沿进行宽松的时序分析,建立时间和保持时间时序如下图所示:

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

#时钟定义

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

#多周期约束检查建立时间

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

#多周期约束检查保持时间

补充:选项-end是对捕获端时钟周期进行移动,-start是对发射端时钟周期进行移动。

5.5 多时钟

5.4.1 整数倍关系

参考5.3部分慢时钟域到快时钟域和快时钟域到慢时钟域

5.4.2 非整数倍关系

最重要的是找出最小公共周期!然后再将时钟扩展到该公共周期。

CLKQ和CLKP之间数据路径的公共周期仅扩展为10ns的公共周期;

CLKM和CLKQ之间数据路径的公共周期为40ns;

而CLKM和CLKP之间数据路径的公共周期也为40ns。

最严苛的建立时间检查是在时钟发起沿和捕获沿之间的最短时间内进行。最严格的保持时间检查是从0ns处的CLKM发起沿到0ns处的CLKP捕获沿。

以CLKM时钟域到CLKP时钟域的数据路径分析为例子:最严苛的建立时间检查就是24ns处的时钟CLKM发起沿以及25ns处的时钟CLKP捕获沿,最严苛的保持时间检查从0ns处的CLKM发起沿到0ns处的CLKP捕获沿。

5.4.3 相移关系

建立时间:距离发射沿最近的捕获沿就是建立时间的检查边沿。

保持时间:建立时间检查的捕获边沿前一个有效边沿就是保持时间的检查边沿。

六、鲁棒性检查

本章节将介绍特殊的STA分析,例如时间借用(time borrowing)、时钟门控(clock gating)和非时序(non-sequential)检查。此外,还介绍了高级STA概念,例如片上变化(on-chip variation)、统计时序(statistical timing)以及功耗和时序之间的折中。

6.1 片上变化(OCV)

6.1.1 降额(derate)

什么是片上变化?

不同制造批次中的工艺参数差异可能会覆盖慢工艺到快工艺,而片上变化是一个芯片上的局部工艺差异和不同的电源电压和温度导致的,该差异远小于不同制造批次之间的差异(称为全局工艺差异)。因此,同一芯片的两个区域可能不在相同的PVT条件下。

为了消除或者减小片上变化,可以通过降额(derate)特定路径的延迟就可以对OCV带来的影响进行建模。

以下以建立时间时序检查为例子进行说明:

set_timing_derate -early 0.9

set_timing_derate -late 1.2

set_timing_derate -late 1.1 -cell_check

什么是early?什么是late?

对于setup Analysis:

- Launch clock: late path

- Data path: late path

- Capture clock: early path

因为 launch clock+Data path 我们都希望为latest(越late OCV越糟糕)

而 capture clock越early越糟糕(越early OCV越糟糕)

对于hold Analysis:

- Launch clock: early path

- Data path: early path

- Capture clock: late path

因为 launch clock+data path 我们都希望越early(越early OCV越糟糕)

而 capture clock 我们都希望为latest(越late OCV越糟糕)

6.1.2 CPPR

由于对公共路径进行不同的derate,这明显是不合规的。CPPR(Common Path Pessimism Removal)表示“公共路径悲观度消除”,通常在路径报告中作为单独的条目列出。

6.1.3 在最严苛的工艺下的建立时间与保持时间时序检查

1.建立时间时序检查——最差PVT条件下的OCV分析

如果在最差情况(worst-case)的PVT条件下执行建立时间检查,则在较晚路径(late path)上就无需降额了,因为它们已经是最差的情况了。但是,可以通过将特定的降额系数应用于较早路径(early path)来使那些路径更快,例如使较早路径加速10%。降额约束可能如下所示:

set_timing_derate -early 0.9

set_timing_derate -late 1.0

set_timing_derate -early 0.8 -clock

2.保持时间时序检查——最佳PVT条件下的OCV分析

通常,保持时间检查是在最佳情况的快速PVT角下执行的。在这种情况下,较早路径无需降额,因为这些路径已经是最快的路径了。但是,可以通过将特定的降额系数应用于较晚路径来使那些路径更慢,例如使较晚路径变慢20%。降额约束可能如下所示:

set_timing_derate -early 1.0

set_timing_derate -late 1.2

6.2 时间借用(Time Borrowing)

时间借用(Time Borrowing)仅发生在锁存器中。通常,应在时钟有效沿之前就在锁存器输入处准备好数据。但是,由于锁存器在时钟处于有效状态时是透明的,因此数据可以晚于有效时钟沿到达,也就是说,它可以从下一个周期借用时间。如果这样借用了时间,则会减少可用于下一级(锁存器到另一个时序单元)的时间。如下图所示:

数据如果在锁存器有效沿延迟到达,则会减少从锁存器到下一个触发器UFF2的可用时间,只有时间Ta可用,而不再是完整的时钟周期。

锁存器时序的第一条规则是:如果数据在锁存器的打开沿之前到达,则寄存器行为将与触发器完全一样。在打开沿捕获数据,而同一时钟沿又将发起数据,作为下一条时序路径的起点。

锁存器时序的第二条规则是:数据在锁存器为透明状态时(在打开沿和关闭沿之间)到达。锁存器的输出将被用作下一级时序路径的起点,而不是时钟引脚。在锁存器处结束的时序路径所借用的时间将决定下一级的发起时间。

以下是锁存器发生time borrowing但没有时序违例的时序报告:

6.3 数据到数据检查

建立时间和保持时间检查也可以在任意两个数据引脚之间进行,这两个都不是时钟引脚。关于触发器建立时间检查的一个重要区别是,数据到数据的建立时间检查是在与发起沿相同的沿上执行的(不同于触发器的常规建立时间检查,其中捕获时钟边沿通常会距离发起时钟沿一个周期)。因此,数据到数据的建立时间检查也称为零周期检查(zero-cycle checks)或同周期检查(same-cycle checks)。

create_clock -name CLKPLL -period 10 -waveform {0 5} [get_ports CLKPLL]

#主时钟定义

set_data_check -from UAND0/A1 -to UAND0/A2 -setup 1.8

set_data_check -from UAND0/A1 -to UAND0/A2 -hold 1.0

#建立时间与保持时间检查,建立时间同周期边沿,保持时间前一个边沿

set_multicycle_path -1 -hold -to UAND0/A2

#也可以用多周期约束使得保持时间检查在同一个边沿

6.4 门控时钟检查

了解门控时钟ICG的工作原理,一般由Latch + 与门构成。具体可以细看这篇文章芯片设计进阶之路——门控时钟。

有两种类型的时钟门控检查:

- 高电平有效时钟门控检查(Active-high clock gating check):当门控单元具有and 或 nand功能时发生。

- 低电平有效时钟门控检查( Active-low clock gating check):当门控单元具有 or或 nor功能时发生。

以高电平有效时钟门控检查为例进行说明:

- 由于为高电平有效,CLKA的信号变化必须落在5ns - 10ns。

- 如果触发器(寄存器)非下边沿有效,则对于建立时间的时序要求严苛(寄存器会有time borrowing)。

- 低电平有效时钟门控检查则不需要满足条件2。

其他几种门控时钟不做介绍,因为门控时钟在工艺库里面有现成模块,重点分析以上ICG模型即可。其余模型可以查看静态时序分析圣经翻译计划——第十章:鲁棒性检查(中)。

参考资料

强烈推荐去B站过完一遍邸老师的静态时序分析基础课文章来源:https://www.toymoban.com/news/detail-605461.html

1.B站邸志雄老师的静态时序分析基础

2.邸志雄老师主页

2.Static Timing Analysis for Nanometer Designs: A Practical Approach. J. Bhasker, Rakesh Chadha. Springer Science Business Media, LLC 2009.

3.集成电路静态时序分析与建模. 刘峰, 机械工业出版社.出版时间:2016-07-01.

4.静态时序分析圣经中文版翻译文章来源地址https://www.toymoban.com/news/detail-605461.html

到了这里,关于静态时序分析STA基础的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[静态时序分析简明教程(二)] 基础知识:建立时间、保持时间、违例修复及时序分析路径](https://imgs.yssmx.com/Uploads/2024/02/421728-1.png)

![[静态时序分析简明教程(八)]虚假路径](https://imgs.yssmx.com/Uploads/2024/02/434351-1.png)