实验简介

本文纯属学习笔记,使用的FPGA是Xilinx的XC7A35TFGG484-1,使用Vivado调用PLL IP核来实现倍频效果,使50Mhz的晶振时钟源倍频到100Mhz、200Mhz和400Mhz。

操作方法

一、点击打开IP核

二、搜索CLOCK选择Clocking Wizard

三、配置过程

Clocking Options

1.MMCM与PLL相比,PLL的时钟质量更高,所以对时钟质量要求较高的时候需要选择PLL,但是一般可以不用纠结。

2.修改Input Frequency为板载晶振频率50Mhz。

Output Clocks

配置倍频时钟、相位、占空比,可以同时打开多个通道,其余的可以保持默认。

注:下面的警告是由于配置的时钟800Mhz已经超过了时钟缓冲器的最大值,XC7A35TFGG484-1的时钟缓冲器的最大频率为464Mhz,锁相环能产生的最大频率为800Mhz。800Mhz是可以在仿真里实现的但是无法在实际中使用,详情见文章末尾

Port Renaming

为Locked信号重命名,保持默认即可。

Locked信号:在刚开始工作之后Locked为低电平,等待时钟稳定之后Locked信号会变成高电平。

PLLE2 Settings

该页面为系统配置的时钟最佳设置,若是将Allow Override Mode勾选上,则可以进行手动修改表中参数,正常使用保持默认即可。

Summary

最后一页是总结,然后点击OK

这一步直接默认点击Generate

四、调用方法

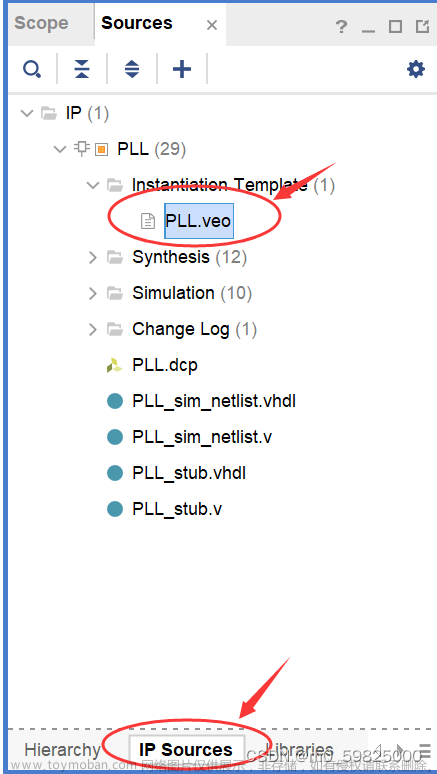

在Sources中找到IP Sources可以看到所有调用的IP核,然后点击打开第一个文件夹Instantiation Template中的PLL.veo文件

然后找到最下面的代码直接复制到顶层文件中例化。

五、仿真验证

顶层代码:

module PLL_TEST(

clk,

reset

);

input clk;

input reset;

wire locked;

wire CLK_800M;

wire CLK_400M;

wire CLK_200M;

wire CLK_100M;

PLL PLL// PLL IP核例化

(

.clk_800M(CLK_800M),

.clk_400M(CLK_400M),

.clk_200M(CLK_200M),

.clk_100M(CLK_100M),

.reset(~reset), //注意这里是~reset

//是要让PLL在FPGA复位的过程中进行初始化

.locked(locked),

.clk_in1(clk)

);

endmodule

testbench代码:

`timescale 1ns / 1ns

module PLL_TEST_TB;

reg clk;

reg reset;

PLL_TEST PLL_TEST(

.clk(clk),

.reset(reset)

);

initial clk = 1;

always #10 clk=~clk;//产生一个50Mhz的时钟

initial begin

reset = 0;

#2000;

reset = 1;

#40000;

$stop;

end

endmodule

仿真结果:

注:800Mhz在实际中不可用!文章来源:https://www.toymoban.com/news/detail-716119.html

附:数据手册

文章来源地址https://www.toymoban.com/news/detail-716119.html

文章来源地址https://www.toymoban.com/news/detail-716119.html

到了这里,关于Vivado PLL锁相环 IP核的使用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!