高速大面阵相机数据采集传输带宽分析与随笔

目前,高速相机的传输瓶颈,受限于传输的带宽。

这里的高速相机指的是大面阵(2048*2048@1000fps)的应用场景。

目前符合条件的CMOS比较少,长光辰芯的4510和4521是符合的。

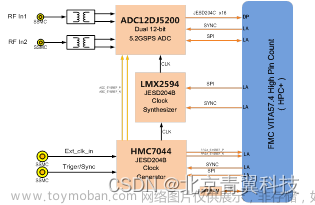

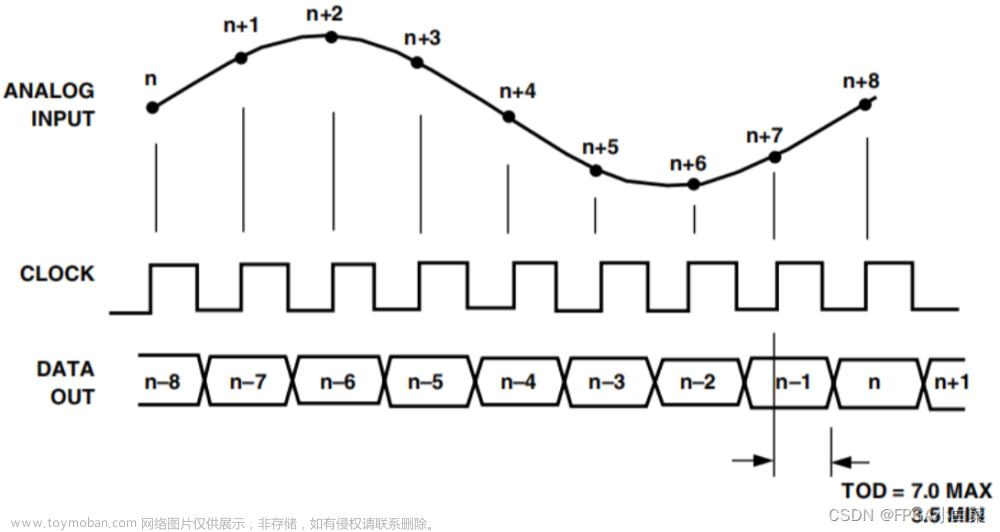

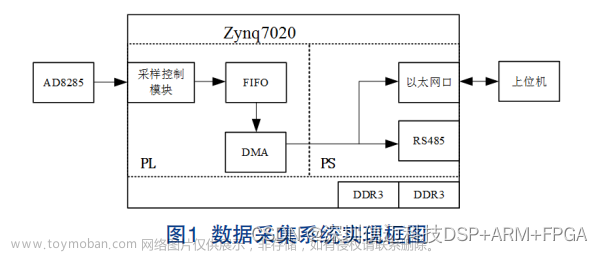

高速相机从CMOS读取数据,到FPGA进行处理,通过高速收发器GT系列,进行大数据量的传输,最后通过传输接口将数据转移到计算机。

这里面传输数据量的瓶颈就是相机对外的传输接口,也就是相机产生的数据怎么才能无损的存到电脑。

之前,高速相机的接口由CameraLink发展到CXP,详见我另一篇的分析:《工业相机常用数据传输协议速率对比(CameraLink,CXP,1/10/100GigE,USB)》

国内关于CXP的资料好少啊,CXP协议也下载不到。感觉路被堵死了。

QSFP28光模块用于100Gige高速相机,还是比较新的。目前国外Emergent和国内的海康在做。

光纤传输多用于互联网的大数据量大带宽大吞吐量的传输,光模块大多用于交换机作为数据中转站,已经是比较成熟的技术了。

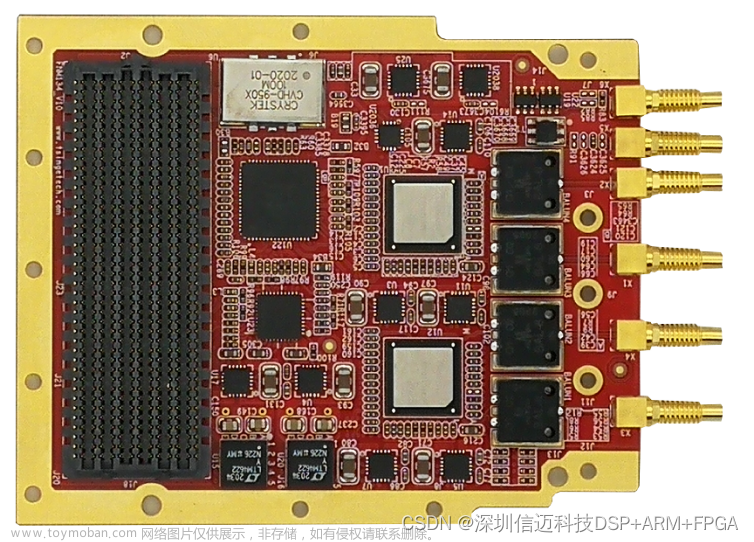

关于高速传输问题,找了一圈,找到了一个米联客的开发板,是带100gige的光模块接口的。

刚好可以用来测试100Gige的传输。文章来源:https://www.toymoban.com/news/detail-730100.html

等测试之后再更新。文章来源地址https://www.toymoban.com/news/detail-730100.html

到了这里,关于高速大面阵相机数据采集传输带宽分析与随笔的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!