1、目的

1、基于Quartus件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。

2、在此基础上,用原理图以及Verilog 编程两种方式,完成4位全加器的设计,对比二者生成的 RTL差别;使用modelsim验证逻辑设计的正确性。

2、了解全加器:

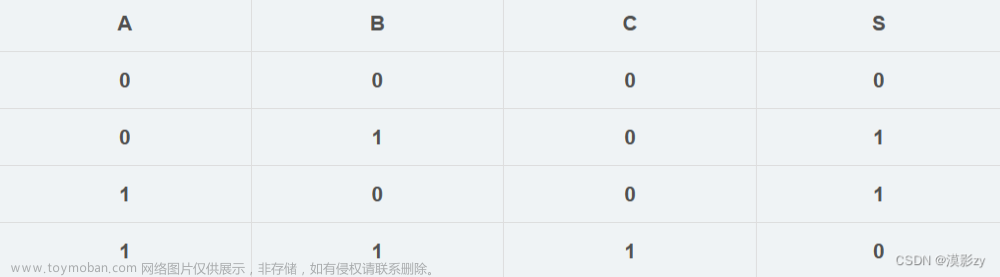

1 1位全加器的真值表:

num1和num2是加数,cin是低位进位,cout是高位进位(我将其理解为溢出),sum是本位和

| num1 | num2 | cin | cout | sum |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

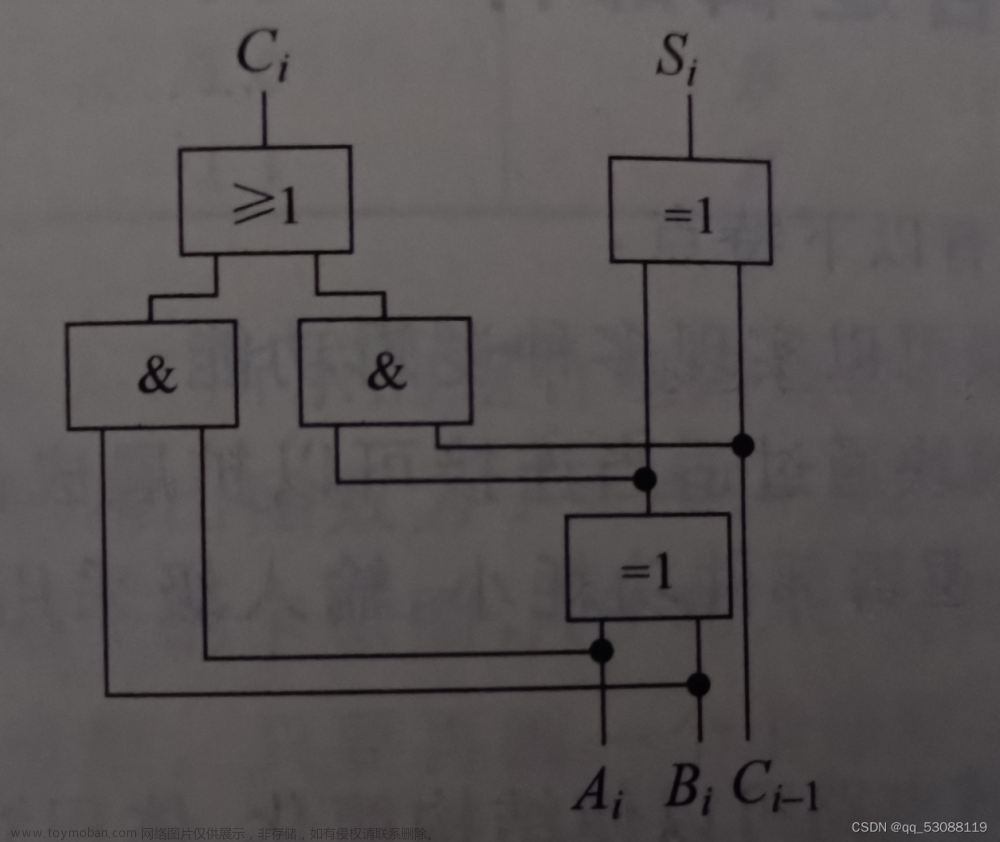

2 输出公式:

sum=num1⊕num2⊕cin

cout=(num1⊕num2)* cin+num1* num2=(num1&num2)∣(num1&cin)∣(num2&cin)

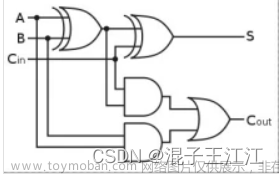

3 原理图:

3、输入原理图实现1位全加器

1 创建工程项目

然后在出现的界面下先Next,填写工程的路径和名称,我这里创建的项目名称为full_add_1bit;然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

2 全加器原理图输入

点击File->New之后会显示如下界面,然后选择被方框框住的选项

然后就会进入到编辑界面,然后按照下面的步骤进行操作。input/output组件也是这样获得的

双击器件可以修改器件名称,为了之后的试验,将两个input分别修改为num1和num2,and2的输出为cout,xor的输出为sum。绘制出来的原理图如下图所示

保存文件(ctrl+s),并编译

等待编译完成之后就可以通过Tool->Netlist Viewers->RTL Viewer,来查看电路图

3 仿真实现

创建一个向量波形文件,File->New,然后选择“University Program VWF”

之后会进入到这个界面,然后按照图片中的步骤进入到信号添加界面

然后先选择Node Finder这个选项,然后再点击List,之后点击’>>',然后点击两次OK,就可以回到上面的那个界面,并且,此时信号也添加成功了。

添加成功之后的界面:

编辑信号:

编辑好之后先保存这个文件,然后点击功能仿真按钮(左边),结果:

时序仿真:

如果出现了错误,返回quartus界面,选择tool->launch simulation library complier进行配置。

4、Verilog实现加法器

1 创建并编写verilog文件

先创建一个verilog文件:

将代码复制到新建的verilog文件中,代码:

module full_add_1bit( // 模块名和文件名相同,文件名和项目名相同

num1,

num2,

cin,

cout,

sum,

);

input num1; // 加数

input num2; // 被加数

input cin; // 低位进位

output cout; // 向高位进位

output sum; // 结果

reg sum;

reg cout;

always @(num1 or num2 or cin) begin

sum = (num1 ^ num2) ^ cin;

cout = (num1 & num2) | (num2 & cin) | (num1 & cin);

end

endmodule

2 查看生成的电路图

先将之前创建的电路图文件从项目中删除,也就是.bdf文件删除,否则会有报错。记得要把新建的verilog文件设置为顶层文件

然后进行编译,当编译完成之后就可以进行电路图的查看了。通过tool->Netlist Viewers->RTL Viewer进行查看。

3 仿真实现

创建一个vwf文件,然后接下来的操作和之前的相同,就不再过多赘述。这里就直接给出仿真结果

功能仿真结果:

时序仿真结果:

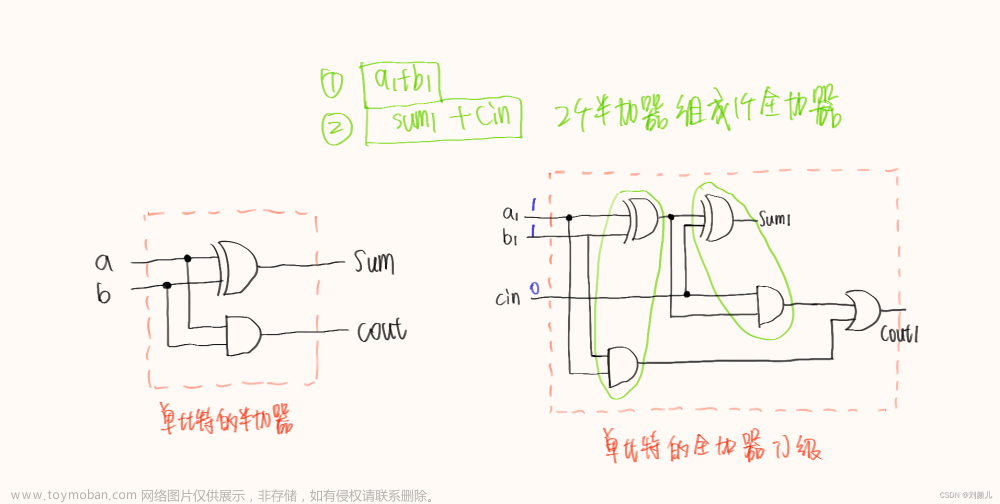

5、拓展:4位全加器

1 4位全加器原理图

这里面使用的组件是封装的,如何封装可以参考:参考博客

2 仿真实现

先创建一个向量波形文件,然后将信号添加进去。这里的操作和前面几乎相同。我们直接看仿真结果:

6、Verilog实现4位全加器

思路

实际上四位全加器和一位全加器的差别并不是很大。我们以一个例子来解释,比如说:这里有两个数,分别是num1=0011,num2=1110。我们算的时候是从最后一位开始一直向前加:

num1的最后一位是1,num2的最后一位是0,两个相加得到01,所以sum的最后一位是1,没有进位;

num1的倒数第二位是1,num2的倒数第二位是1,没有低位进位,相加得10,所以sum的倒数第二位是0,向前进位为1;

num1的第二位是0,num2的第二位是1,低位进位为1,所以相加得10,sum的第二位为0,向前进位为1;

num1的第一位是0,num2的第一位是1,低位进位为1,所以相加得10,sum的第一位为0,向前进位为1;

所以,通过上面的步骤,我们可以得到sum=0001,向前进位cout=1。

1 创建文件,编写代码

先创建一个verilog文件,并将下面代码复制到文件中

module four (

num1,

num2,

cin,

cout,

sum

);

input [3:0] num1;

input [3:0] num2;

input cin;

output cout;

output [3:0] sum;

reg cout;

reg [3:0] sum;

reg add;

always @(num1 or num2 or cin)

begin

// 第一位

sum[0] = (num1[0] ^ num2[0]) ^ cin;

cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin);

add = cout;

// 第二位

sum[1] = (num1[1] ^ num2[1]) ^ add;

cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add);

add = cout;

// 第三位

sum[2] = (num1[2] ^ num2[2]) ^ add;

cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add);

add = cout;

// 第四位

sum[3] = (num1[3] ^ num2[3]) ^ add;

cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add);

add = cout;

end

endmodule

2 查看电路

记得将verilog文件设置为顶层文件之后再进行操作

3 仿真实现

7、ModelSim验证4位全加器

1 创建源文件和testbench文件

源文件,four.v

module four (

num1,

num2,

cin,

cout,

sum

);

input [3:0] num1;

input [3:0] num2;

input cin;

output cout;

output [3:0] sum;

reg cout;

reg [3:0] sum;

reg add;

reg [1:0] cnt;

always @(num1 or num2 or cin)

begin

// 第一位

sum[0] = (num1[0] ^ num2[0]) ^ cin;

cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin);

add = cout;

// 第二位

sum[1] = (num1[1] ^ num2[1]) ^ add;

cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add);

add = cout;

// 第三位

sum[2] = (num1[2] ^ num2[2]) ^ add;

cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add);

add = cout;

// 第四位

sum[3] = (num1[3] ^ num2[3]) ^ add;

cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add);

add = cout;

end

endmodule

testbench文件,four_tb.v

module four_tb ();

reg [3:0] num1;

reg [3:0] num2;

reg cin;

wire cout;

wire [3:0] sum;

four uut(

.num1(num1),

.num2(num2),

.cin (cin),

.cout(cout),

.sum (sum)

);

initial

begin

num1 <= 4'b0000; num2 <= 4'b0000; cin <= 0;

#10 num1 <= 4'b0000; num2 <= 4'b0000; cin <= 1;

#10 num1 <= 4'b0101; num2 <= 4'b0001; cin <= 0;

#10 num1 <= 4'b1000; num2 <= 4'b0100; cin <= 0;

#10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 0;

#10 num1 <= 4'b1100; num2 <= 4'b0100; cin <= 1;

#10 num1 <= 4'b0011; num2 <= 4'b0000; cin <= 1;

#10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 1;

end

endmodule

2 创建ModelSim项目

打开ModelSim之后创建一个项目,将刚才创建的两个文件加入到项目当中。然后将文件进行编译,成功之后就可以进行进行验证了。

3 验证结果

如果要把每一种情况都进行测试的话肯定是不可能的,所以这里只测试几条数据,以验证程序逻辑的正确性。根据验算,这里的结果是没有问题的。

8、总结

总的来说,这次的试验还是比较简单的。相当于是熟悉一下这些软件和代码的编写。为之后的学习打下一定的基础。文章来源:https://www.toymoban.com/news/detail-753041.html

9、参考

https://blog.csdn.net/qq_43279579/article/details/115480406

https://blog.csdn.net/m0_46653805/article/details/118736483文章来源地址https://www.toymoban.com/news/detail-753041.html

到了这里,关于FPGA实现1位全加器和4位全加器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!