鱼弦:CSDN内容合伙人、CSDN新星导师、全栈领域创作新星创作者 、51CTO(Top红人+专家博主) 、github开源爱好者(go-zero源码二次开发、游戏后端架构 https://github.com/Peakchen)

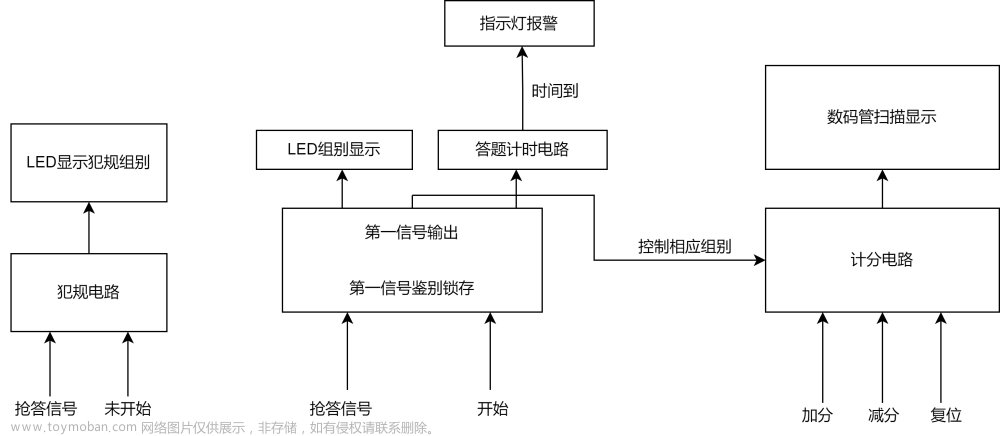

智能电子抢答器可容纳4组参赛者抢答,每组设一个抢答钮。 ③ 电路具有第一抢答信号的鉴别和锁存功能。在主持人将复位按钮按下后开始抢答,并用EDA实训仪上的八段数码管显示抢答者的序号,同时扬声器发出“嘟嘟”的响声,并维持3秒钟,此时电路自锁,不再接受其他选手的抢答信号。 ④ 设计一个计分电路,每组在开始时设置为100分,抢答后由主持人计分,答对一次加10分,答错一次减10分。 ⑤ 设计一个犯规电路,对提前抢答和超时抢答者鸣喇叭示警,并显示犯规的组别序号

原理详细解释:文章来源:https://www.toymoban.com/news/detail-758122.html

四人抢答器是一个基于状态机的数字电路系统。它通过状态的切换和计时器的控制来实现抢答的逻辑。具体的工作流程如下:文章来源地址https://www.toymoban.com/news/detail-758122.html

- IDLE状态: 初始状态,等待抢答开始按钮的触发。

- QUIZ状态: 抢答开始后,将抢答者的序号显示在数码管上,同时启动蜂鸣器计时器。

- LOCK状态: 在QUIZ状态下,如果有抢答信号,进入LOCK状态,同时锁定其他抢答信号,启动计分计

到了这里,关于fpga开发基于verilog HDL的四人抢答器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!