🦄🦄欢迎大家来学习数字电路——时序逻辑电路。

🦄🦄在这里我们会讲解二进制计数器、十进制计数器和集成计数器74LS161,希望通过我们的学习会让你更明白数字电路中的奥秘。

目录

🔑一、计数器

🏆1.二进制计数器

(1)异步二进制加法计数器

(2)同步二进制加法计数器

🏆2.十进制计数器

(1)电路组成

(2)工作过程

🏆3.集成计数器

(1)74LS161芯片的引脚排列和图形符号

一、计数器

能累计输入脉冲个数的数字电路称为计数器,计数器是数字电路中应用十分广泛的单元逻辑电路,除直接用作技术、分频、定时外,还经常应用于数字仪表、程序控制、计算机等领域。

计数器的种类很多,

①按计数的进位体制不同,可分为二进制、十进制和N进制计数器等;

②按计数器中数值的增、减情况,可分为加法计数器、减法计数器、可逆计数器;

③按计数器中各触发器状态转换时刻的不同,可分为同步计数器和异步计数器。

1.二进制计数器

定义:

在计数脉冲作用下,各触发器状态的转换按二进制的编码规律进行计数的数字电路称为二进制计数器。

构成计数器电路的核心器件是具有计数功能的JK触发器。可将JK触发器接成计数状态,如图所示:

(1)异步二进制加法计数器

如图所示电路是用三个JK触发器连成的异步3位二进制加法计数器。

图中各位触发器的端接在一起作为计数器的直接复位输入信号;计数脉冲加到最低位触发器 的FF0端,其他触发器的CP依次受低位触发器Q端的控制。各触发器接收到负跳变脉冲信号时状态就翻转。

波形如图所示:

🎈🎈工作过程:

计数前,在复位端先输入一负脉冲,使=000,这一过程称为清零,清零后,应使=1,才能正常计数。

当第一个计数脉冲CP作用后,该脉冲的下降沿使触发器FF0的由0态转为1态,其他两个触发器因没有CP下降沿的作用,仍保持0态,所以当第一个CP作用后,计数器状态为=001。

当第二个计数脉冲CP作用时,触发器FF0翻转,由1态转为0态,的下降沿加到FF1的时钟脉冲输入端,使从0态转为1态,上升沿变化对触发器FF2无效,状态保持不变,所以当第二个CP作用后,计数器状态为=010。

依此类推,当第七个CP作用后计数器状态为111,当第八个CP作用后计数器又回到000状态,完成一次计数循环。

(2)同步二进制加法计数器

如图所示为同步3位二进制加法计数器:

各级触发器的CP端连在一起,受同一个时钟脉冲控制,显然各触发器状态的翻转与时钟同步,故称同步计数器。

2.十进制计数器

二进制计数器结构简单,运算方便。但在许多场合,使用十进制计数器较符合人们的习惯。所谓十进制计数器是在计数脉冲作用下各触发器状态的转换按十进制数的编码规律进行计数的数字电路。

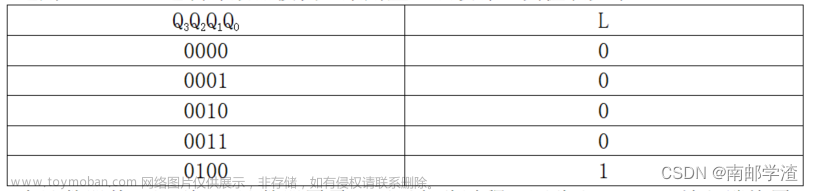

用二进制数码表示十进制数的方法称为二—十进制编码(即BCD码)。十进制数有0~9共10个数码,至少要用4位二进制数。而4位二进制数有十六个状态,表示1位十进制数只需要十个状态,因此需要去掉其中的六个状态。在十进制计数器中常采用8421BCD码的编码方式进行计数。

8421编码见表:

(1)电路组成

异步十进制加法计数器电路由4位二进制计数器和一个用于计数器清零的门电路组成,与二进制加法计数器的主要差异是跳过了二进制数码1010~1111的6个状态。

(2)工作过程

计数器输入0~9个计数脉冲时,工作过程与4位二进制异步计数器完全相同,第九个计数脉冲后=1001。

当第十个计数脉冲到来后,计数器状态为=1010,此时,与非门输入全1,输出为0,使各触发器复位,即=0000, 同时使与非门输出又变为1,计数器重新开始工作。 从而实现8421BCD码十进 制加法计数的功能。

3.集成计数器

集成计数器是将触发器及有关门电路集成在一块芯片上,使用方便且便于扩展。中规模集成同步计数器类型很多,常见的4位十进制同步计数器有74LS160、74LS162、74LS196、CC40192等;4位二进制同步计数器有74LS161、74LS163、74LS169、74LS191等。

(1)74LS161芯片的引脚排列和图形符号

74LS161芯片的引脚排列和图形符号如图所示:

① 异步清零

当异步置0控制端=0时,不管其他输入端的状态如何,无论有无时钟脉冲,计数器输出将直接置零,称异步清零。

② 同步预置数

当=1时,同步置数控制端=0,且在CP上升沿作用时,并行输入数据被置入计数器的输出端,使= 。由于这个操作要与CP同步,所以又称为同步预置数。

真值表如表所示:

③保持

当时==1、时,输出保持不变。这时若=0、=1,则进位输出信号CO保持不变;若=1、=0,进位输出信号CO为低电平。

④计数

当 ====1时,CP为上升沿有效时,实现加法计数功能。文章来源:https://www.toymoban.com/news/detail-781584.html

【时序逻辑电路】结束了,下期我们开启新篇章——【脉冲波形的产生与变换】😁😁文章来源地址https://www.toymoban.com/news/detail-781584.html

到了这里,关于【时序逻辑电路】——计数器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!