系列文章目录

以太网(二)PHY、网卡、SWITCH介绍 [link]

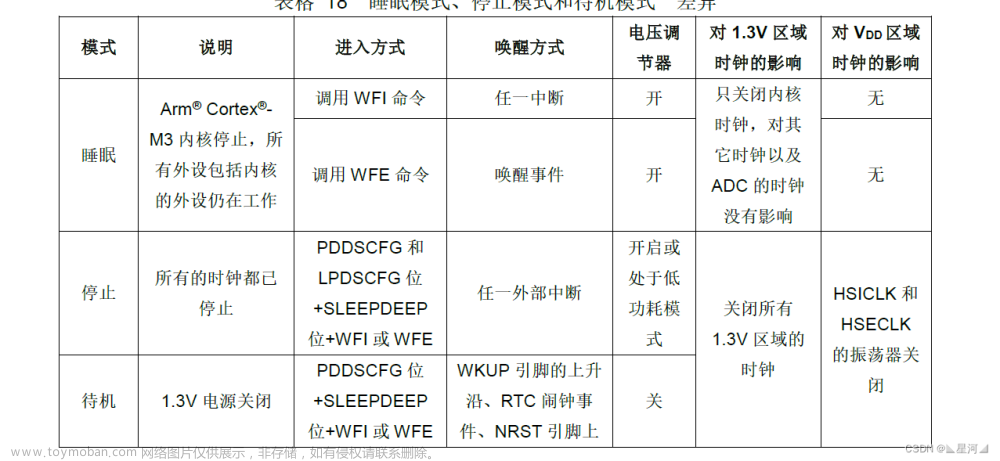

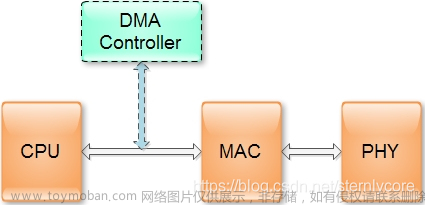

1、CPU/MAC/PHY 硬件架构

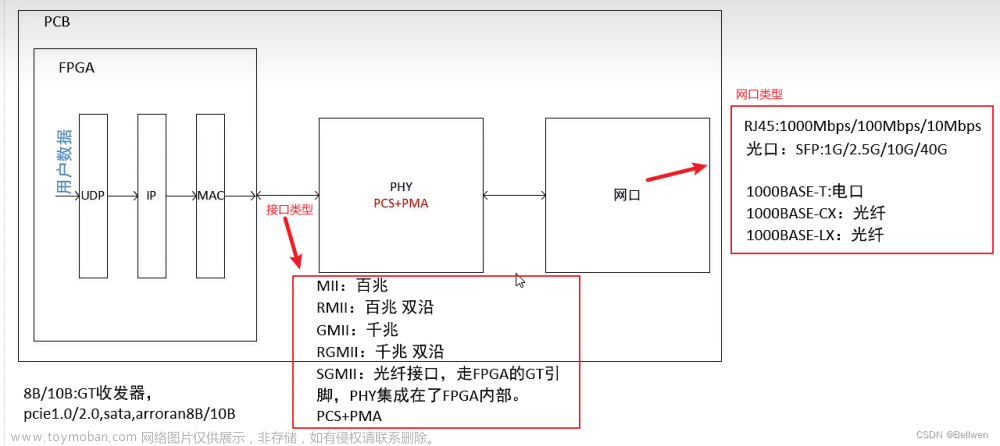

以太网是由CPU,MAC,PHY三部分组成的,如下图示意:

但是,在实际的设计中,CPU、MAC和PHY三部分并不一定是独立分开的,存在以下三种方式:

- MAC 与 PHY集成在CPU中,目前来说并不多见。

- MAC集成在CPU中,而PHY 采用独立芯片,这种比较常见。

- MAC 和 PHY不集成在CPU 中,二者集成在同一芯片(形成独立的网卡),这种也比较常见。

由于PHY 整合了大量模拟硬件,而 MAC 则是典型的全数字器件。考虑到芯片面积及模拟/数字混合架构的原因,将MAC集成进CPU而将PHY留在片外,这种结构是最常见的。 下图是网络接口内部结构图,虚框表示CPU,MAC集成在CPU中,PHY芯片通过MII接口与CPU上的MAC连接。

MAC 及 PHY 工作在 OSI 七层模型的数据链路层和物理层。具体如下:

IEEE802.3 标准文档下载链接[link]。标准文档很长,分为很多 section,大概第一部分是 10Mb/s 以太网(其中有关于 MAC 的规范),第二部分是 100BASE-T 100Mb/s 基带网络介绍,第三部分是 1000 Mb/s 基带网络介绍,第四部分是 10 Gb/s 基带网络介绍。但是,并不是说每部分都是独立的。

2、网卡(MAC和PHY)工作原理

网卡工作在OSI模型中物理层和数据链路层,物理层的芯片称之为 PHY,数据链路层的芯片称之为 MAC控制器。

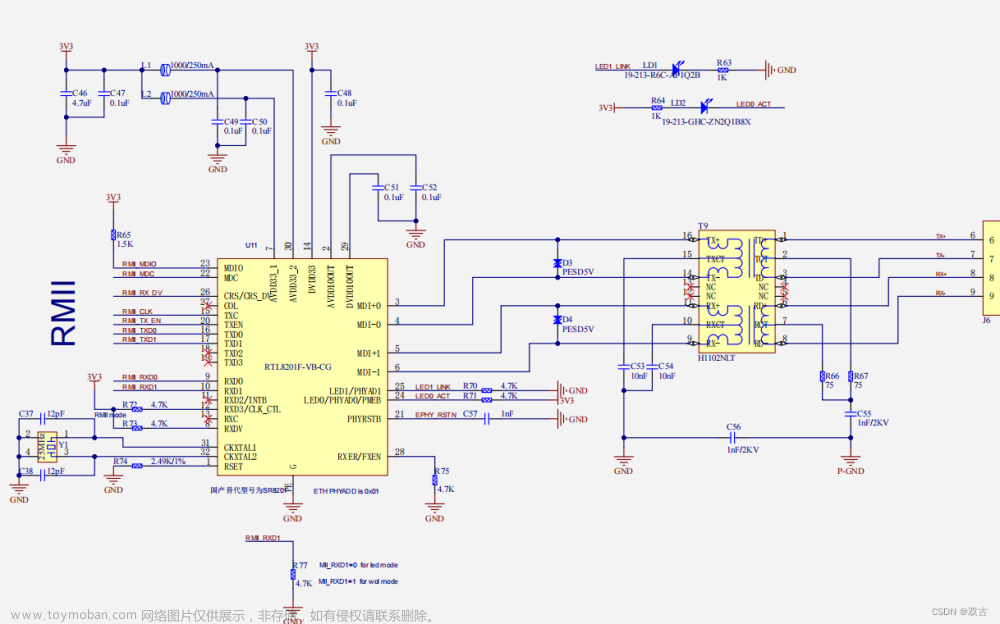

物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能。以太网卡中。很多网卡的这两个部分是做到一起的。他们之间的关系是PCI总线接MAC总线,MAC接PHY,PHY接网线(当然也不是直接接上的,还有一个变压装置)。

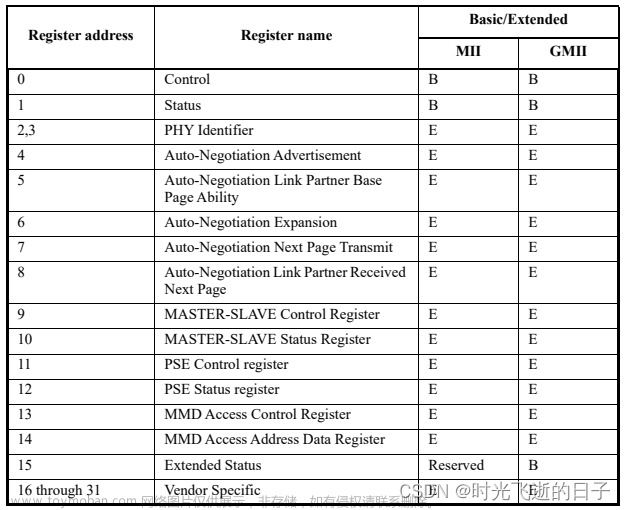

PHY 和 MAC 通过 MII/GigabitMII(Media Independed Interfade,媒体独立接口) 连接,IEEE定义的标准协议。MII传递了网络的所有数据和数据的控制,而MAC对PHY的工作状态的确定和对PHY的控制则是使用SMI(Serial Management Interface) 界面通过读写PHY的寄存器来完成的。

PHY里面的部分寄存器也是IEEE定义的,PHY把目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,例如连接速度,双工的能力等。当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等。

不论是物理连接的MII接口和SMI总线,还是PHY的状态寄存器和控制寄存器遵循IEEE规范。因此不同公司的MAC和PHY一样可以协调工作。当然为了配合不同公司的PHY特有的一些功能,驱动需要做相应的修改。

来源链接: [link]

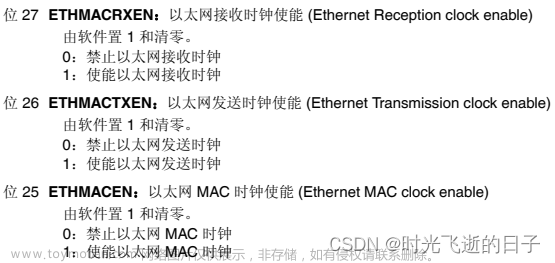

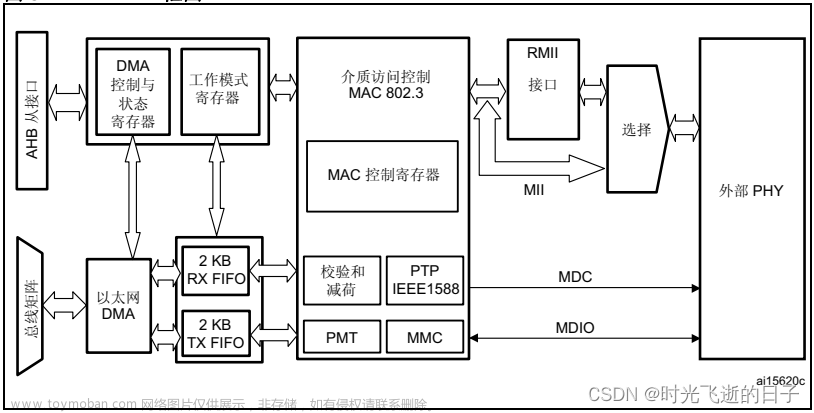

3、什么是 MAC

MAC(Media Access Controler) 即媒体访问控制层协议(GMAC:Gigabit Media Access Controller)。MAC由硬件控制器和MAC通信协议构成。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。MAC硬件框图如下图所示:

在发送数据的时候,MAC 协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC 协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至 LLC(逻辑链路控制)层。该层协议是以太网 MAC,由 IEEE-802. 3 以太网标准定义。最新的 MAC 同时支持 10Mbps 和100Mbps 两种速率。

以太网数据链路层其实包含 MAC(介质访问控制)子层和 LLC(逻辑链路控制)子层。一块以太网卡 MAC 芯片的作用不但要实现 MAC 子层和 LLC 子层的功能,还要提供符合规范的 PCI 界面以实现和主机的数据交换。

MAC 从 PCI 总线收到 IP 数据包或者其他网络层协议的数据包后,将之拆分并重新打包成最大 1518Byte、最小 64Byte 的帧。这个帧里面包括了目标 MAC 地址、自己的源 MAC 地址和数据包里面的协议类型(比如IP数据包的类型用 80 表示),最后还有一个DWORD(4Byte)的 CRC 码。

目的 MAC 地址通过 ARP 学习得到,并以IP 地址和 MAC 地址的对应关系保存在主机系统中,叫做 ARP 表,通过 arp -a 命令查看 ARP 表。

收到数据帧的时候也是一样,做完 CRC 校验以后,如果没有 CRC 效验错误,就把帧头去掉,把数据包拿出来通过标准的接口传递给驱动和上层的协议栈。最终正确的达到我们的应用程序。

4、什么是 PHY

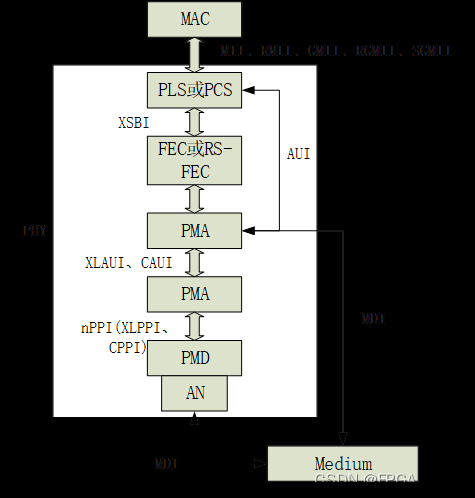

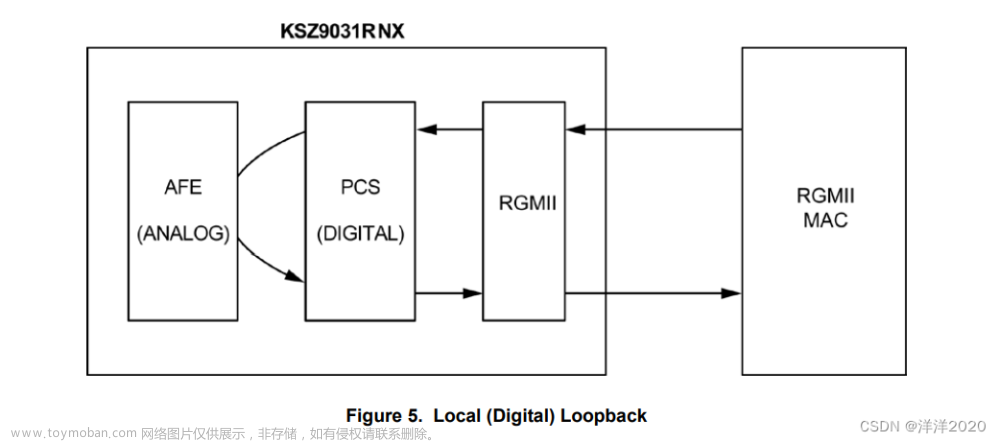

PHY(Physical Layer) 是 IEEE802.3 中定义的一个标准模块,STA(station management entity,管理实体,一般为MAC 或 CPU)通过 SMI(Serial Manage Interface)对 PHY 的行为、状态进行管理和控制,而具体管理和控制动作是通过读写 PHY 内部的寄存器实现的。PHY的基本结构如下图:

PHY 在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据),每4bit就增加1bit的检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则(10Based-T的NRZ编码或100based-T的曼彻斯特编码)把数据编码,再变为模拟信号把数据送出去,收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能,它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去.如果两个碰巧同时送出了数据,那样必将造成冲突,这时候冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据。

关于 PHY 寄存器介绍参见[链接]。

5、什么是 MII

MII(Media Independent Interface) 即媒体独立接口,MII 接口是 MAC 与 PHY 连接的标准接口。它是 IEEE-802.3 定义的以太网行业标准。MII 接口提供了 MAC 与 PHY 之间、PHY 与 STA(Station Management)之间的互联技术,该接口支持 10Mb/s 与 100Mb/s 的数据传输速率,数据传输的位宽为 4 位。MII 接口如下图所示:

MAC 通过MIIM 接口(MII 的 Management Interface)读取PHY 状态寄存器以得知目前PHY 的状态。例如连接速度、双工的能力等。也可以通过 MIIM设置PHY的寄存器达到控制的目的。例如流控的打开关闭、自协商模式还是强制模式等。MII以4位半字节方式传送数据双向传输,时钟速率25MHz。其工作速率可达100Mb/s。当时钟频率为2.5MHz时,对应速率为10Mb/s。MII接口虽然很灵活但由于信号线太多限制多接口网口的发展,后续又衍生出RMII,SMII等。文章来源:https://www.toymoban.com/news/detail-801718.html

6、MAC 与 PHY 接口类型汇总表

参考文章:

以太网物理介质介绍[link]

以太网MII接口类型大全[link]

详解 MAC 地址、MAC 协议、MAC 控制器[link]

网卡构造:MAC与PHY的关系,GMAC介绍[link]

千兆网媒体访问控制(GMAC)[link]

网络相关接口汇总描述[link]

以太网中的 MAC、MII、PHY 详解 [link]

MAC/PHY/MII/RMII/GMII/RGMII基本介绍 [link]文章来源地址https://www.toymoban.com/news/detail-801718.html

到了这里,关于以太网(一)MAC、MII、PHY 介绍的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!