高亚军老师的这本书《AMD FPGA设计优化宝典》,他主要讲了两个东西:

第一个东西是代码的良好风格;

第二个是设计收敛等的本质。

这个书的结构是一个总论,加上另外的9个优化,包含的有:时钟网络、组合逻辑、触发器、移位寄存器、存储器、乘加运算单元、状态机、扇出、布线拥塞。大部头的书看起来比较痛苦,我简化的方式,选择触发器一章入手,这个平时有点了解,也觉得看完会用上的概率大一些。这章是书的第4章,复位桥方面的内容,接前面的我的文章:

复位桥

把异步的复位变成同步的复位

1 多时钟域复位桥电路

每个时钟域都要有自己的复位信号,而且复位信号要与该时钟域的时钟同步。如下图所示,复位信号在进入每个时钟域前都先进行异步复位同步释放操作,使得复位信号和该时钟域的时钟同步。

2 代码部分

我把原书代码的system Verilog版本 变成Verilog版本,理解一下精髓。注意的是: 参数N要控制在8以内

(* ASYNC_REG = “TRUE” ) reg [N-1:0] bridge;**// ( ASYNC_REG = “TRUE” ) 布局时放置在同一个sclice的意思*

(* ASYNC_REG = “TRUE” *) reg [1:0] bridge_dly;

always@(posedge clk, posedge aset) begin

if(aset) begin

bridge <= ‘1;//所有位都赋值1

end else begin

bridge <= { bridge[N-2:0], 1’b0};//除了最高位之外的低N-1位,左移一位,最低位赋值0

end

end

always@(posedge clk) begin

bridge_dly[0] <= bridge[N-1];//bridge最高位赋值给bridge_dly的最低位

bridge_dly[1] <= bridge_dly[0];//bridge_dly的最高位是最低位延一拍, bridge_dly[1]也输出作为同步复位

end

这些代码的作用是将输入的异步复位信号aset展宽(aset是高电平有效)(aset原宽度为1,展宽的宽度是N),并将aset展宽后的信号同步到目标时钟(clk)下。文章来源:https://www.toymoban.com/news/detail-831112.html

3 改善布局

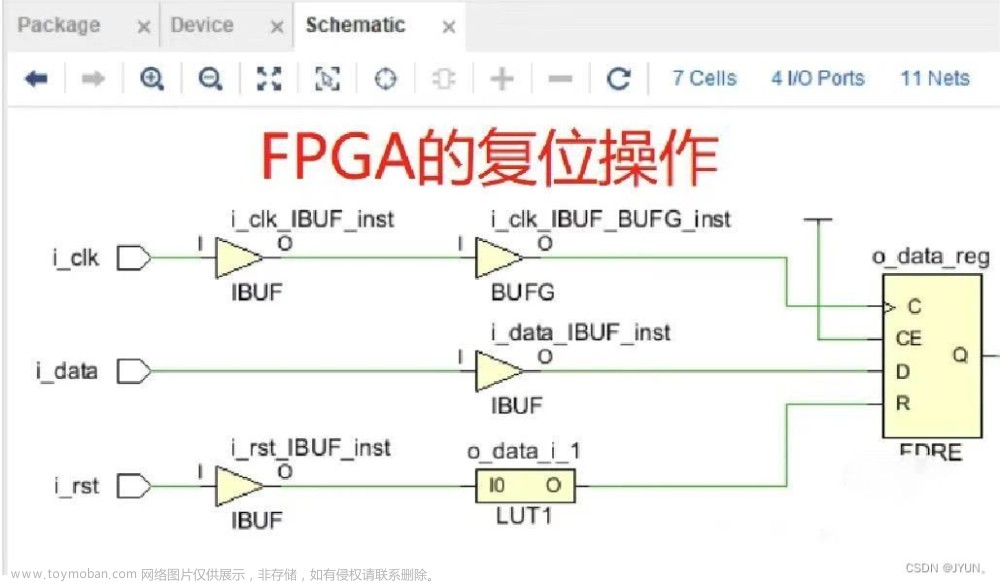

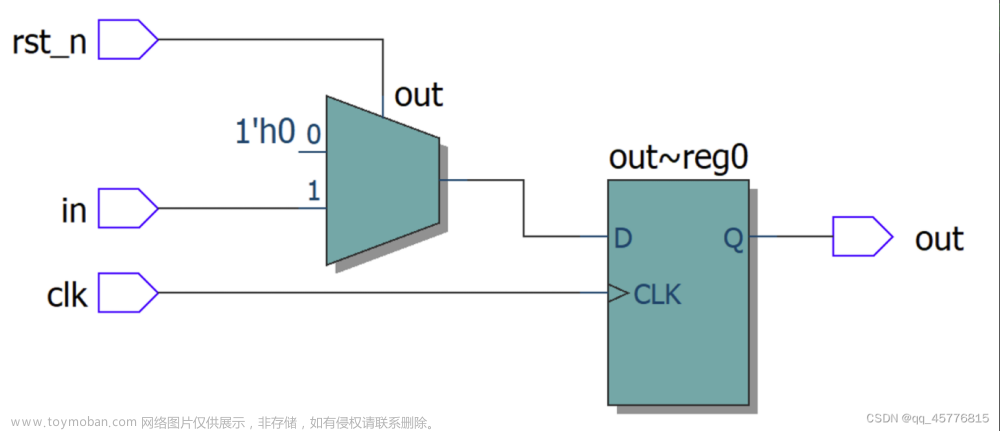

同步复位比较好,因为综合时工具可以根据控制集的要求将其搬移到数据路径上,对改善布局质量很有帮助。

同步复位受时钟控制,因此时钟可以过滤复位信号上的毛刺从而防止触发器误动作。异步复位不受时钟控制,没法过滤毛刺从而可能导致触发器误动作。 文章来源地址https://www.toymoban.com/news/detail-831112.html

文章来源地址https://www.toymoban.com/news/detail-831112.html

到了这里,关于AMD FPGA设计优化宝典笔记(4)复位桥的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!