我们都知道,FPGA中的拥塞有:全局拥塞,短线拥塞和长线拥塞。

今天我们就来看短线拥塞的一种解决方案:Reduce MUXF Mapping。

UltraScale的CLB资源

在介绍Reduce MUXF Mapping,我们需要知道什么是MUXF,这就得从UltraScale的CLB说起。

我们都知道,在7系列的FPGA中,每个CLB有两个Slice;而在UltraScale系列中,每个CLB中只有一个Slice,Slice又分成了两种类型SliceL(Logic)和SliceM(Memory),其中SliceM中的LUT可以当作分布式RAM来使用。

每个Slice中包含:

-

6输入2输出LUT * 8,其中SliceM中的LUT可配置为512bits的Distributd RAM和256bits的Shift Registers

-

Flip-Flops * 16

-

Carry8 * 1

-

Wide Multiplexer,即MUXF*

- MUXF7 * 4

- MUXF8 * 2

- MUXF9 * 1

什么是MUXF?

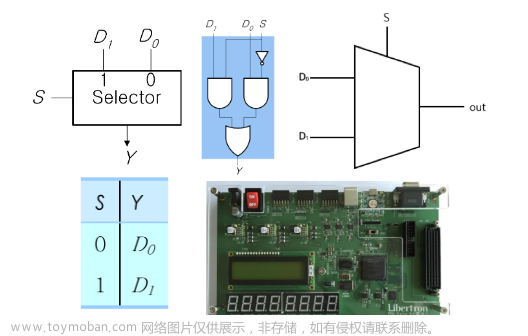

在Ultrascale系列的FPGA中,MUXF*是指MUXF7,MUXF8和MUXF9,需要注意的是:他们不是7选1,8选1和9选1的MUX,具体解释如下图:

我们再具体解释一下:

- MUXF7有F7MUX_AB、F7MUX_CD、F7MUX_EF、F7MUX_GH这4个,每个MUXF7均可以与其后面的2个相邻的LUT构成一个8:1 MUX;

- MUXF8有F8MUX_BOT和F8MUX_TOP,每个MUXF8均可以与其后面的邻近2个F7MUX以及后面的邻近4个LUT构成一个MUX16_1;

- MUXF9只有一种就是F9MUX,可以与其后面的所有的F7MUX、F8MUX、LUT构成一个MUX32_1。

下面的图是由F8MUX_BOT,两个F7MUX和4个LUT构成的16:1的MUX,图中的D触发器是可选的,是为了减少时序收敛的难度。

MUXF在什么场景下有优势?

从上面的图中,我们可以看出来,如果实现一个16:1的MUX,在配合MUXF的情况下,只需要一个Slice就可以完成;在一个Slice中完成的逻辑,我们都可以当成是一个logic level;而如果完成由LUT来实现16:1的MUX,则需要多级logic level,因此MUXF的其中一个优势就是可以减少logic level。

MUXF的第二个优势就是节省功耗,在FPGA中,LUT本身的功耗就是要高一些,再加上对于wide multiplexer,所需要的LUT数量也比较多,因此采用MUXF的方式,对于功耗方面是有优势的。

MUXF在什么场景下有劣势?

既然MUXF可以减少logic level,那为什么vivado还有一个专门的选项muxf_remap来优化MUXF呢?

这是因为MUXF在布局时会与八个 LUT组合在一起,这种组合导致 CLB 输入的利用率很高,增加了路由需求,但是会在网表连接复杂时限制了布局的灵活性,从而可能导致更高的路由拥塞,导致时序不好收敛。

下面这个图就展示了将MUXF替换成LUT3之后的效果,需要注意的是,这种替换会增加功耗,仅在我们想收敛时序时使用。

如何使用该优化指令

在 Vivado 中,opt_design 命令提供了一个可选的 MUX 优化阶段,可以将 MUXF* 结构重新映射为 LUT原语以提高路由能力。我们可以使用 -muxf_remap 选项重新映射所有的 MUXF* 单元。或者,可以在拥塞区域的选择单元上设置 MUXF_REMAP 属性为 TRUE,以限制 MUX 重映射的范围。任何设置了 MUXF_REMAP 属性为 TRUE 的 MUXF* 单元将在 opt_design 期间自动触发 MUX 优化阶段,并被重新映射为 LUT。文章来源:https://www.toymoban.com/news/detail-857634.html

set_property BLOCK_SYNTH.MUXF_MAPPING 0 [get_cells inst_name]

FPGA技术交流群,添加微信:z02091168文章来源地址https://www.toymoban.com/news/detail-857634.html

到了这里,关于FPGA时序优化之Reduce MUXF Mapping的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!