一、概述

1.什么是高速电路?

- 一般认为:高速电路频率≥50MHz且这部分频率电路达到1/3。

- 客观的讲:考虑到上升下降沿及延迟,当信号的传输路径大于1/6倍传输信号波长时,认为是高速信号。

- 因此,信号的传输延迟大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应,即为高速电路。

2.高速信号

- 一般地,信号上升时间的典型值可以通过器件手册得到,而信号的传播时间在PCB上由实际布线长度决定,PCB板上每英寸的传输延时约为0.167ns(约5~6inch/ns)。

- 如果过孔多,器件管脚多,信号线上设置的约束多,延迟增大。

- 通常高速逻辑器件的信号上升时间大约为0.2ns。

设Tr为信号上升时间,Tpd为信号线传播延时。如果:

- Tr>4Tpd,信号落在安全区域;

- 2Tpd < Tr ≤ 4Tpd,信号落在不确定区域;

- Tr ≤2Tpd,信号落在问题区域。

3.高速设计

- 电源滤波,均匀分配电源,降低系统噪声

- 匹配信号线,减少反射

- 降低走线间串扰

- 减小地弹效应

- 阻抗匹配

- … …

4.整体设计思路

- 对单板宏观整体了解

- 对硬件研发流程节点了解

- 对设计规范熟悉

- 能平衡SI、SI、EMC、成本、周期等要求

A、SI/PI/EMC设计指南

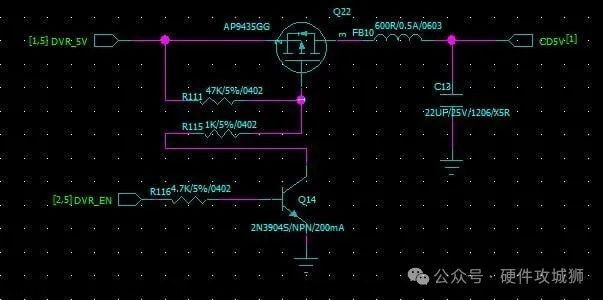

B、开关电源PCB设计指南

C、射频/模拟PCB设计指南

D、接口电路PCB设计指南

E、时钟电路PCB设计指南

高速PCB设计流程:

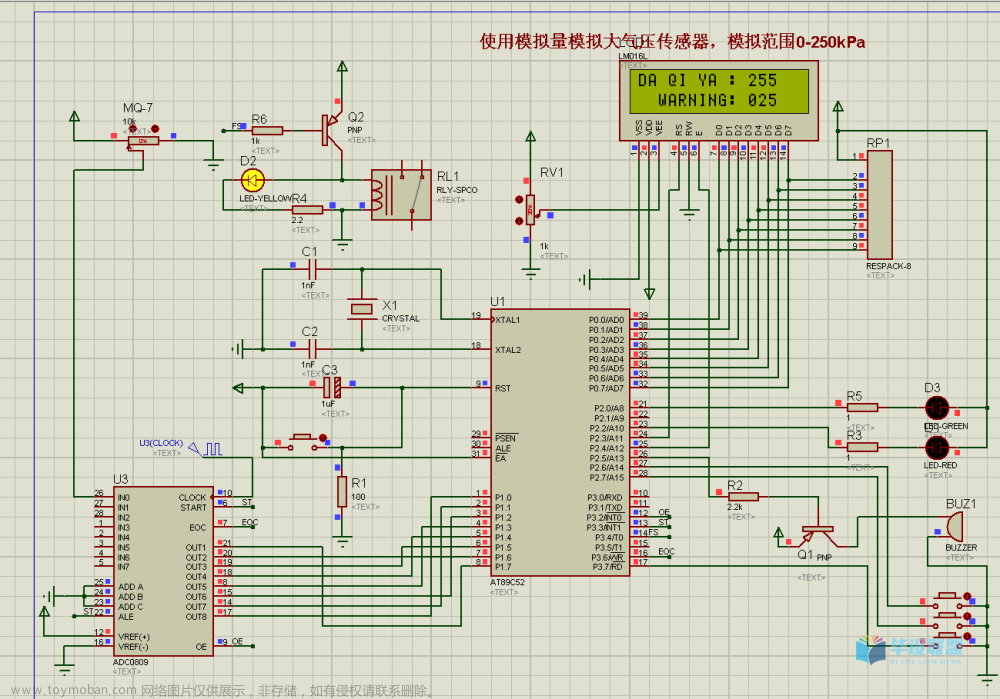

- 单板整体电路分析:对单板主要芯片方案、电源方案、主要总线、信号流向、电源树、接口类型、工艺方案、EMC方案等做整体了解和规划

- 预布局、前仿真分析:在综合考虑满足信号质量、EMC、热设计、DFM等方面的基础上,把主要器件合理的摆放到PCB上

- 布局布线:在满足信号质量、DFM、EMC等规则要求下,完成器件摆放和信号互连

- 后仿真验证:Sl仿真、PI仿真、热仿真

- 工艺评审:利用Valor等先进工具进行DFM

二、高速PCB叠层与阻抗设计

1.PCB层叠理论基础

- 信号线阻抗:介质厚度对阻抗影响大、尽量减小线宽、加大线距(3W原则),降低串扰

- 信号返回路径:

-低速中,电流沿着最小电阻路径流动

-高速中,电流沿着最小电感路径流动 - 电源、地平面:

-为数字信号的转换提供稳定的参考电压

-为所有的逻辑器件提供电源

-控制信号之间的串扰 - 电源完整性要求:电源对地保持低阻抗,电源阻抗为

-D为电源地平面间距,W为平面重叠的面积 - 平面隔离技术:推荐使用额外的地平面而不是电源平面来隔离布线

2.叠层设计原则

参考

PCB_3.PCB叠层

PCB_4.确定PCB层压

3.阻抗设计精度

- 阻抗精度要求一般在±10%,严格的±5%

- 控制阻抗的连续性比片面追求阻抗值更重要

4.PCB设计时带来的阻抗不连续

- 线宽突变

- 走线跨分割

- 过孔换层

- 分支结构

- 连接器器件管脚

三、高速PCB布局布线设计

1.布局思路

- 提前规划,绘制框图

- 预布局(可不受板框、DRC限制)

- 模块化布局

- 布局优化

2.布局设计规则

对规则熟悉且有书面条例进行检查对照。文章来源:https://www.toymoban.com/news/detail-400290.html

3.Fanout(扇出)设计

QFN

模块调整时把扇出做好,扇出时保证布线通道(器件本体下,器件Pin下,空隙处)。

PIN间距0.5MM

- 单片时信号线尽量往外扇出,电源地尽量往里扇出,就近放置滤波电容

- 双片时正反对贴,共用电源、地孔,就近放置滤波电容

BGA

0.5BGA扇出,一阶HDI

- BGA可以使用自动fanout,后面再根据具体情况调整孔的位置;-由于阻抗控制关系,盲孔出来到埋孔的线应该尽量短。

- 0.5BGA扇出,盲孔尽量打在四个焊盘的中间;不要打在焊盘上,不然加工要做电镀填孔,难度成本大

0.4BGA扇出,一阶HDI。

- 0.4BGA的只能打在盘上。

4.布局思路

- 规则驱动设计

- 关键信号优先处理

- 整板布线

- 电源、地处理

- 等长绕线

- 布线优化

5.布线设计规则

对规则熟悉且有书面条例进行检查对照。

四、高速PCB仿真介绍

1.高速PCB仿真的目的

- 确定关键信号的链路阻抗

- 确定关键信号、总线的链路长度

- 确定阻抗匹配方案

- 确定总线拓扑结构

- 提前预估信号质量

- 确保硬件设计质量

2.高速PCB仿真流程

- 信息获取:了解信号类型、特征及相关要求,获取模型

- 规划评估:规划高速链路布线路径,估算最长最短的大致走线长度,预先选定几种板材,并获取相关参数

- 设计叠层:根据信号阻抗,单板空间和板厚,确定层数,计算差分阻抗,创建传输线模型

- 设计过孔:在满足设计和加工要求的情况下,确定过孔结构、回流孔、扫描频率或变量等参数,分析仿真结果,输出过孔模型

- 绘制原理图:根据规划,搭建串行链路原理图,设置相应参数

- 仿真分析:分析仿真结果,优化走线、过孔、均衡等参数

3.高速PCB仿真痛点和难点

- 仿真软件的使用比较复杂

- 许多器件的仿真模型很难获取

- 对SI的理论知识没有吃透

- 仿真软件的价格昂贵

4.高速PCB仿真应用

- 高速串行链路仿真(如PCIE)

- 高速并行链路仿真(DDR系统级验证)

- 电源仿真(分析确定载流宽度等)

相关内容及图片为《电巢》课程的学习记录,侵删。文章来源地址https://www.toymoban.com/news/detail-400290.html

到了这里,关于【高速PCB电路设计】1.高速PCB设计概述的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!