同步计数器和异步计数器的区别

1.同步计数器的外部时钟端都连在一起,而异步计数器没有

2.同步计数器在外部信号到来时触发器同时翻转,而异步计数器的触发器为串行连接,工作频率较低

3.异步计数器输出状态的建立,要比CP慢一个传输时间,容易存在竞争冒险

竞争冒险:当信号通过导线和门电路,将会产生时间延迟,到达门输入端的时间有先有后这就叫竞争;逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲现象就冒险;

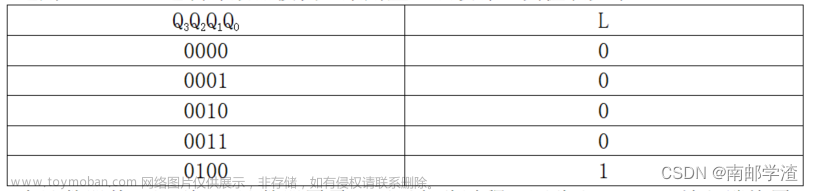

同步二进制计数器--74LS161集成计数器

ABCD:并行数据预置输入端

QA QB QC QD:数据输出端

ENP、ENT:计数控制端

CLK:时钟脉冲输入端文章来源:https://www.toymoban.com/news/detail-462949.html

RCO:进位端(进位输出高电平)文章来源地址https://www.toymoban.com/news/detail-462949.html

到了这里,关于数电:计数器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!