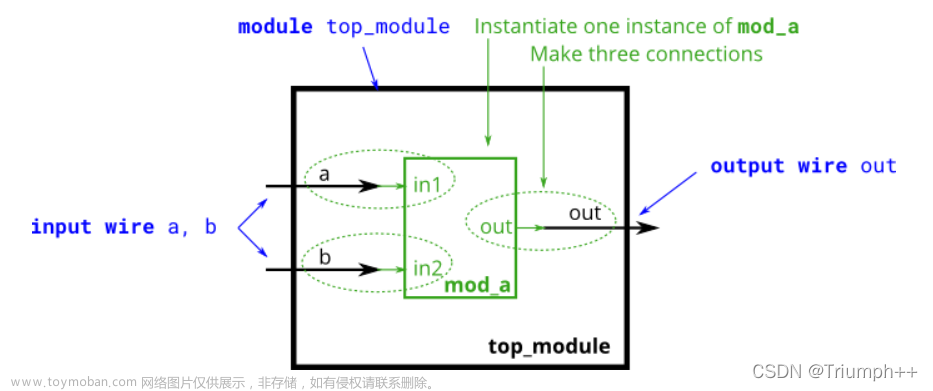

verilog语法中的模块例化

FPGA的设计通常都是由很多个模块组成,有顶层模块、高层模块和子模块之分,模块例化的功能即为连接这些模块。

以数码管显示代码为例,根据要实现的功能,需在顶层模块中对计时模块和数码管静态显示模块分别例化。

计时模块代码如下:

module time_count(

clk,

rst_n,

flag

);

parameter MAX_NUM = 50000000

......

endmodule数码管静态显示模块部分代码如下:文章来源:https://www.toymoban.com/news/detail-504883.html

module seg_led_static (

clk,

rst_n,

add_flag,

sel,

seg_led

);

......

endmodule则顶层模块中的例化代码如下:文章来源地址https://www.toymoban.com/news/detail-504883.html

module seg_led_static_top (

sys_clk,

sys_rst_n,

sel,

seg_led

);

parameter TIME_SHOW = 50000000;

wire add_flag;

time_count #(

.MAX_NUM (TIME_SHOW)

)u_time_count(

.clk(sys_clk),

.rst_n(sys_rst_n),

.flag(add_flag)

);

seg_led_static u_seg_led_static (

.clk(sys_clk),

.rst_n(sys_rst_n),

.add_flag(add_flag),

.sel(sel),

.seg_led(seg_led)

);

......

endmodule到了这里,关于verilog基础-模块例化的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Verilog语法-模块module[Day2学习笔记]](https://imgs.yssmx.com/Uploads/2024/02/608941-1.png)