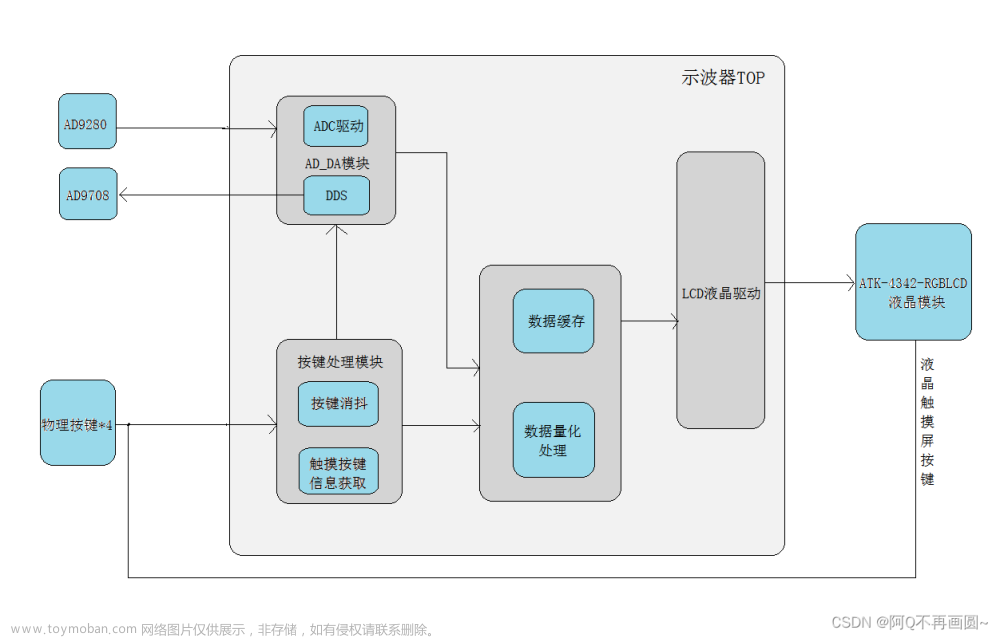

1. 示波器带宽简述

示波器有很多不同规格,确定了可捕获和测量信号的准确度。但是示波器的主要规格是其带宽。

2. 带宽的定义

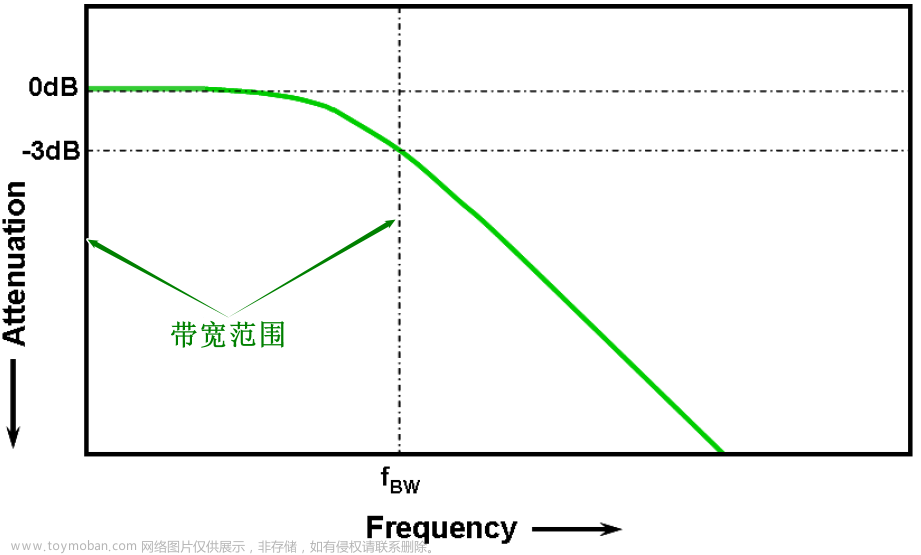

所有示波器都具有以较高频率展示的低通频率响应,如下图所示。大多数带宽规格为 1 GHz 以及更低的示波器通常具有高斯频率响应。示波器高斯频率响应近似于单极点低通滤波器,即您可能已在某些电路课程中学过而且可能绘制为波特图的一些内容。

2.1 示波器高斯频率响应

按

3dB衰减输入信号的最低频率被视为示波器的带宽 (fBW)。以-3 dB频率执行信号衰减会转换为约-30%幅度误差。换句话说,如果将1 Vp-p,100 MHz正弦波输入100 MHz带宽示波器中,则使用此示波器测量的峰峰值电压会在约700 mVp-p (因为 -3 dB = 20 Log [0.707/1.0])的范围内。因此无法对示波器带宽周围具有超高频率的信号执行准确测量。

2.2 总结得到以下带宽描述

带宽是示波器的基本指标,和放大器带宽的定义一样,是所谓的

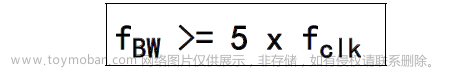

3dB点,即在示波器的输入端加入正弦波,幅度衰减为实际幅度的70.7%时的频率点称为带宽。也就是说使用100MHz带宽的示波器测量1V,100MHz的正弦波,最终通过示波器观察得到的幅度只有0.707V,当然这还只是正弦波的情形。因此我们在选择示波器的时候,所以为了达到一定的测量精度,应该选择信号最高频率 5 倍的带宽。

带宽经验法则:

示波器的带宽应至少比测试信号中的最快数字时钟频率高五倍。如果示波器符合此标准,则最高可捕获信号衰减最小的第五谐波。在确定数字信号的整体形状的场景下此信号分量非常重要。

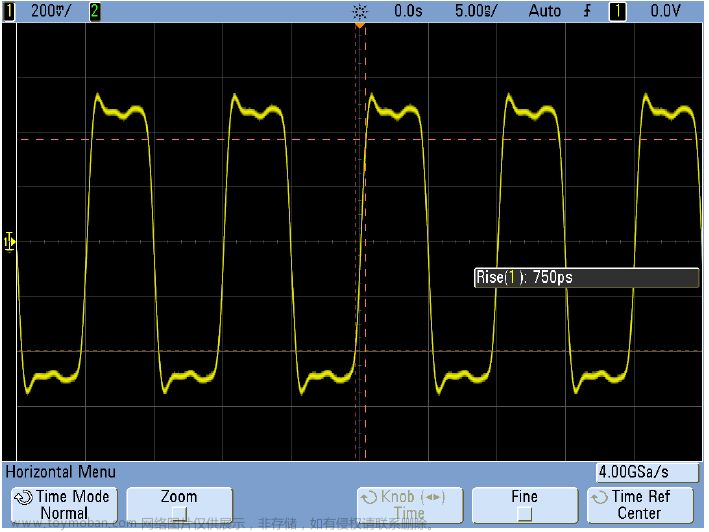

3. 带宽影响上升时间

示波器的带宽规格密和上升时间规格切相关。具有高斯类型的频率响应的示波器的上升时间约为

0.35/fBW(这个数据是基于 10% 至 90% 标准)。但是需要记住,示波器的上升时间不是示波器能够准确测量的最快边沿速度。而是当输入信号具有理论上无限快的上升时间 (即0 ps) 时,示波器可能产生的最快边沿速度。尽管从实际角度看,这一理论规格无法测试 (主要因为由于脉冲发生器不具备无限快速边沿),但是可以通过输入边沿速度比示波器的上升时间规格快 5 到 10 倍的脉冲,来测试示波器的上升时间。文章来源:https://www.toymoban.com/news/detail-536301.html

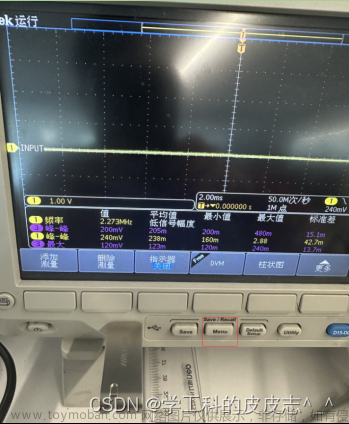

4. 带宽与信号影响

在 100 MHz 带宽示波器上捕获的 100 MHz 数字时钟信号

在 500 MHz 带宽示波器上捕获的 100 MHz 数字时钟信号

在 1 GHz 带宽示波器上捕获的 100 MHz 数字时钟信号文章来源地址https://www.toymoban.com/news/detail-536301.html

到了这里,关于示波器带宽的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!