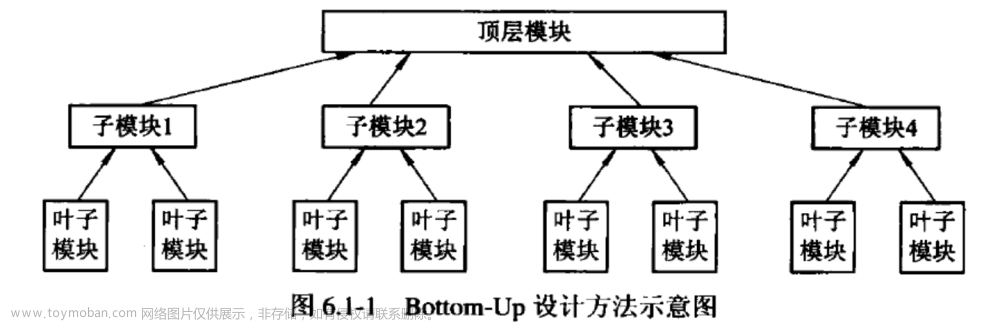

Cadence(virtuoso)集成电路设计软件基本操作——建库的两种方法

学习目标

- 如何在cadence中建立设计库

- 建库的具体步骤及各步骤作用

建立库菜单

参照新工艺文件建立库

Compile an ASCII technology file

Reference existing technology libraries

Attach to an existing technology library

和第二项类似,不同的是第二项相当于复制,此项相当于引用。文章来源:https://www.toymoban.com/news/detail-564654.html

Do not need process information

即不参照工艺文件,选此项将无法进行仿真和版图设计,不采用文章来源地址https://www.toymoban.com/news/detail-564654.html

到了这里,关于Cadence(virtuoso)集成电路设计软件基本操作——建库的两种方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!