本文介绍一个FPGA开源项目:UDP RGMII千兆以太网通信。该项目在我之前的工作中主要是用于FPGA和电脑端之间进行图像数据传输。本文简要介绍一下该项目的千兆以太网通信方案、以太网IP核的使用以及Vivado工程源代码结构。

Vivado 的 Tri Mode Ethernet MAC IP核需要付费才能使用,因此本文提供完整工程源码。文章末尾有该工程源码获取方式,有需要的小伙伴可以收藏、分享一下。

一、软硬件平台

- 软件平台:Vivado 2017.4;

-

硬件平台:XC7K410TFFG900-2;

二、RGMII接口

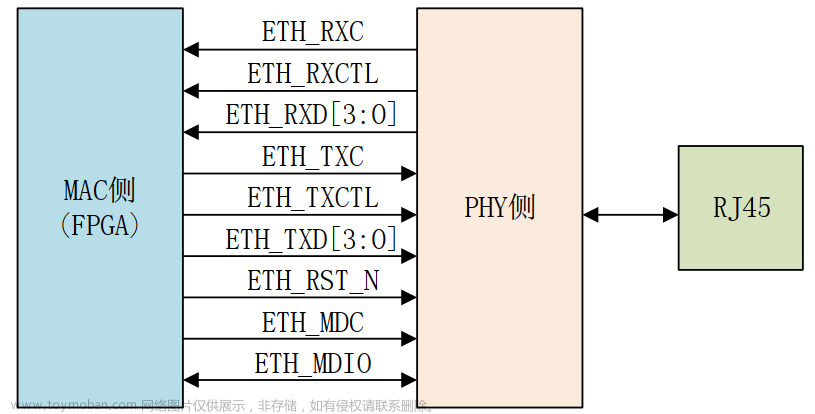

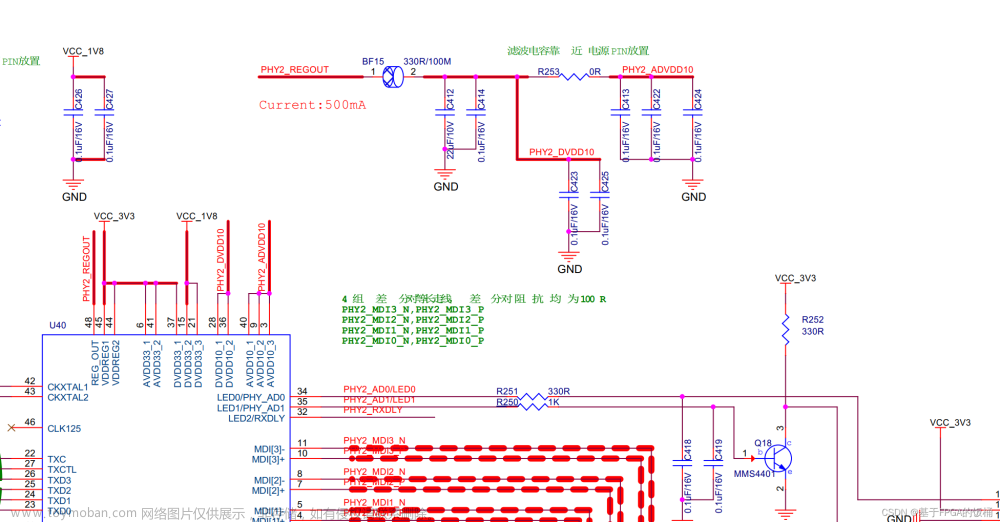

本设计采用 RGMII 接口的 88E1512 芯片。RGMII 接口的主要优势在于,它可以同时适用于1000M、100M、10M三种速率,并且接口占用引脚数较少。

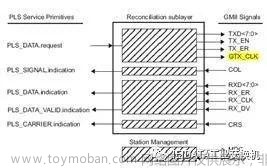

RGMII 使用 4bit 数据接口采用上下沿 DDR(Double Data Rate)的方式在一个时钟周期内传输 8bit 数据信号,即上升沿发送或者接收数据的低4位[3:0],下降沿发送或者接收数据的高4位[7:4]。同理,使用 1bit 控制接口采用 DDR 的方式在一个时钟周期内传输 2bit 控制信号。

- 发送端:tx_clk,tx_d[3:0],tx_ctrl;

-

接收端:rx_clk,rx_d[3:0],rx_ctrl;

-

三种速率模式

RGMII 接口适用于1000M、100M、10M三种传输速率。

当工作于1000M时,时钟信号TXC和RXC均为 125MHz,4bit数据信号上下沿值均有效,控制信号上下沿值也均有效。

当工作于100M时,时钟信号TXC和RXC均为25MHz,4bit数据信号只有上升沿值[3:0]有效,相当于此时数据信号切换为单沿SDR(Single Data Rata)4位输模式。控制信号仍为上下沿有效。

当工作于10M时,时钟信号TXC和RXC均为2.5MHz,数据信号和控制信号的使用和100M速率时完全相同。

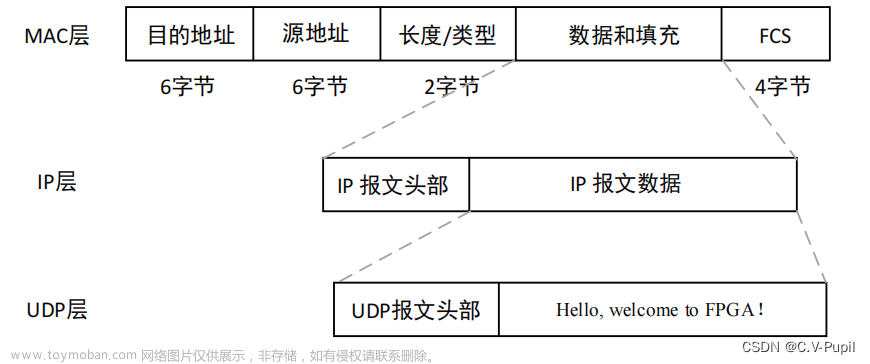

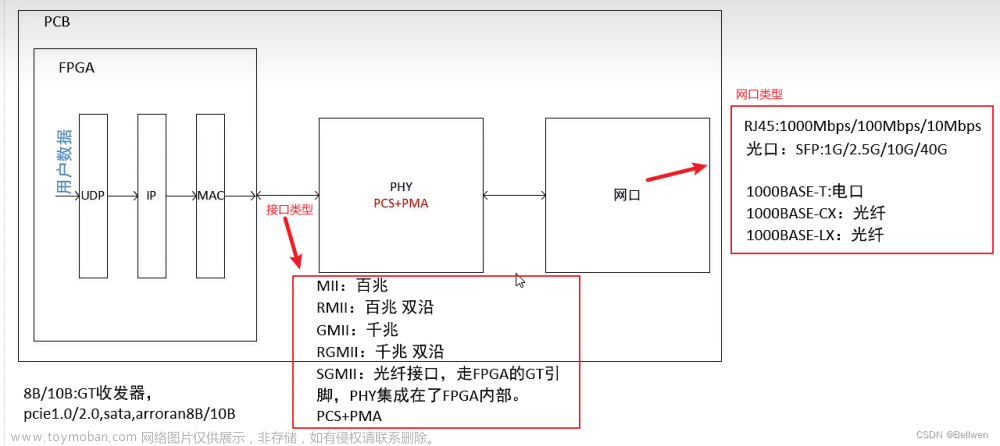

三、UDP通信方案

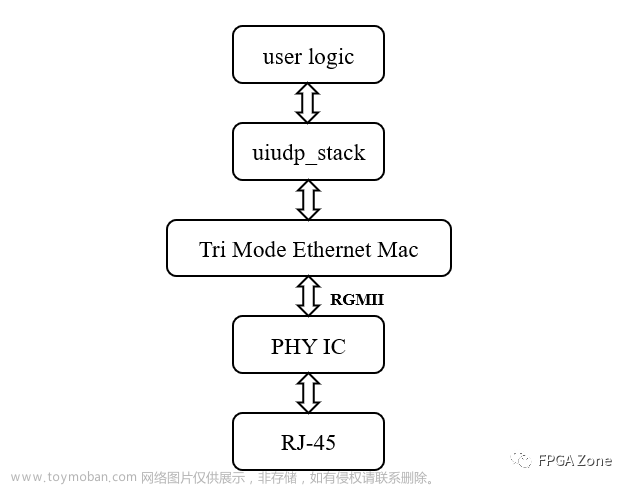

该以太网通信方案参考米联客例程设计,硬件接口采用RGMII,IP核调用Vivado 的 Tri Mode Ethernet MAC。通信方案如下图所示,最上层为用户逻辑模块,用于处理和使用解析后的以太网通信数据;uiudp_stack 模块采用米联客例程提供的协议栈网表文件;FPGA 以太网IP核采用Tri Mode Ethernet Mac;PHY芯片采用 88E1512;最后 RJ-45 接口通过网线与上位机连接。

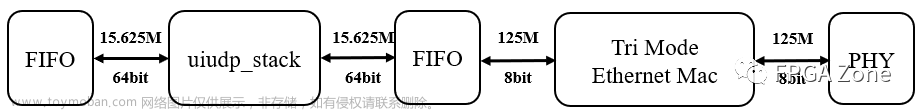

下图为以太网数据环路传输测试方案,在电脑上通过网络调试助手向FPGA发送任意小于1472字节长度的UDP数据包。由于Tri Mode Ethernet Mac IP核接口数据流为8bits/125M,而uiudp_stack为64bits/15.625M,因此需要在中间插入FIFO缓存模块,进行数据位宽转换以及数据跨时钟域处理。

四、工程源码结构

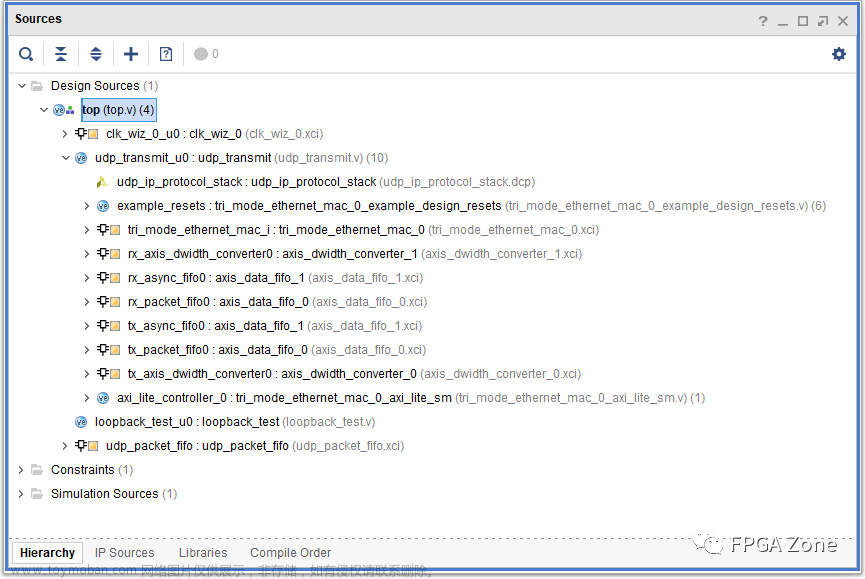

下图是该项目 Vivado 工程源码结构:

其中,

-

udp_transmit:UDP以太网数据收发模块;

-

loopback_test:UDP以太网数据回环传输测试模块;

-

tri_mode_ethernet_mac_0_axi_lite_sm:用于配置、读取以太网IP核寄存器等。

五、IP核参数配置

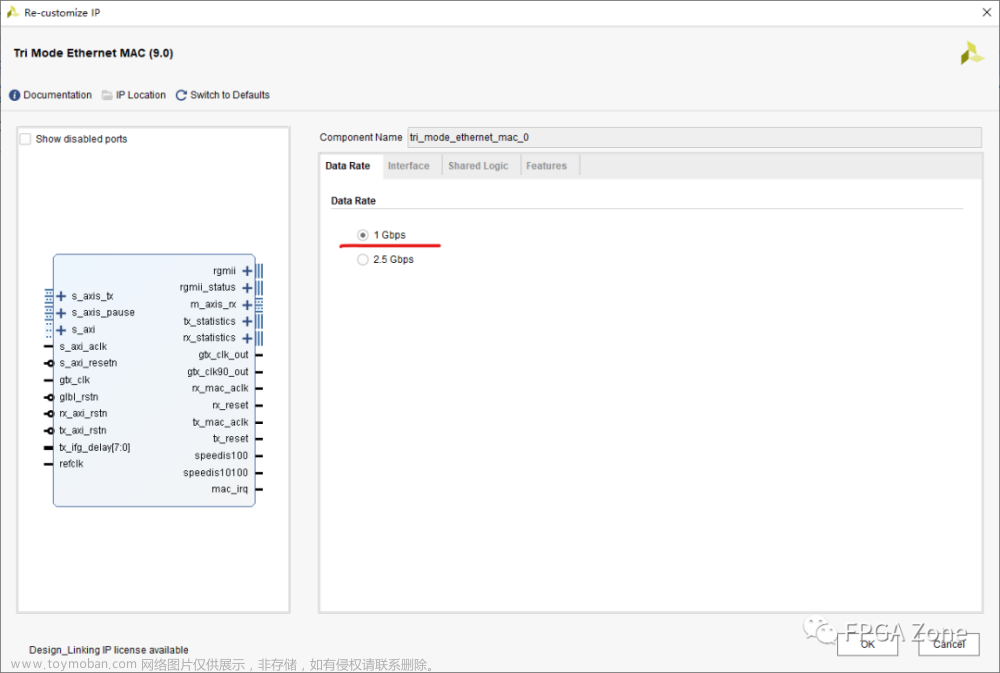

使用千兆通讯,因此将速率设为 1Gbps;

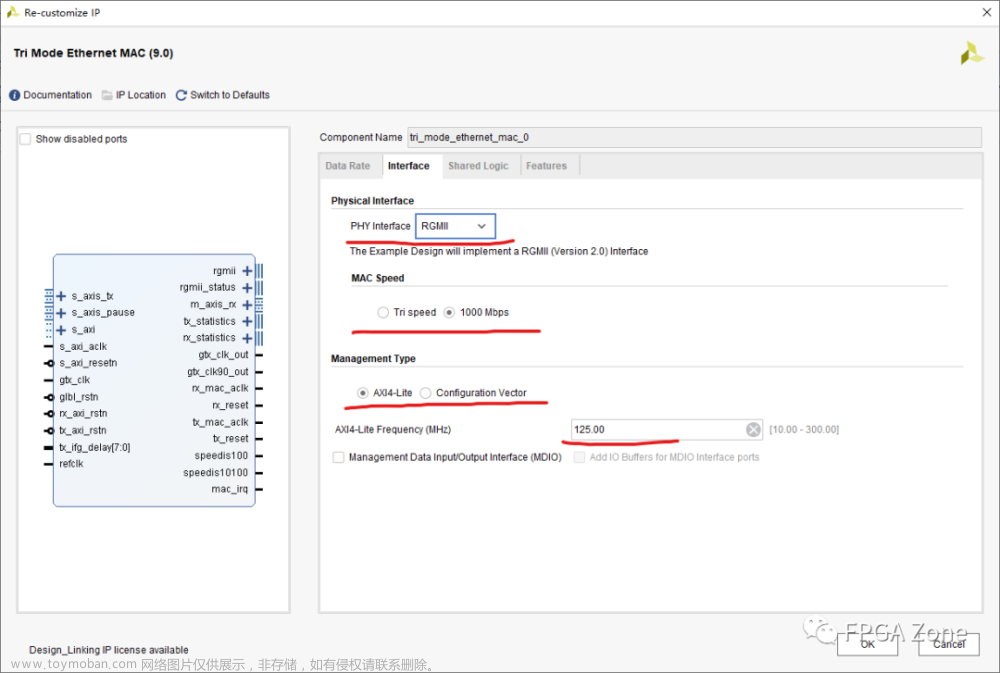

接口参数配置如下:

另外,有关 UDP 协议栈 uiudp_stack 的详细信息这里不再介绍,其pdf文档和源码一起提供,有需要的小伙伴可以自己去查阅。

六、其它注意事项

-

PHY芯片 复位信号:上电后将复位信号拉高;

-

FPGA RGMII输出 I/O 口 电平标准:配置成 SSTL 电平标准。文章来源:https://www.toymoban.com/news/detail-631065.html

七、源码获取方式

需要该工程源码的小伙伴,请下载我的 资源:《FPGA优质开源项目获取方式》 ,里面有Vivado工程源码免费获取方式。 或者点击链接,跳转到原文获取:《FPGA优质开源项目 - UDP RGMII千兆以太网》。文章来源地址https://www.toymoban.com/news/detail-631065.html

到了这里,关于FPGA优质开源项目 - UDP RGMII千兆以太网的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!