0、前言

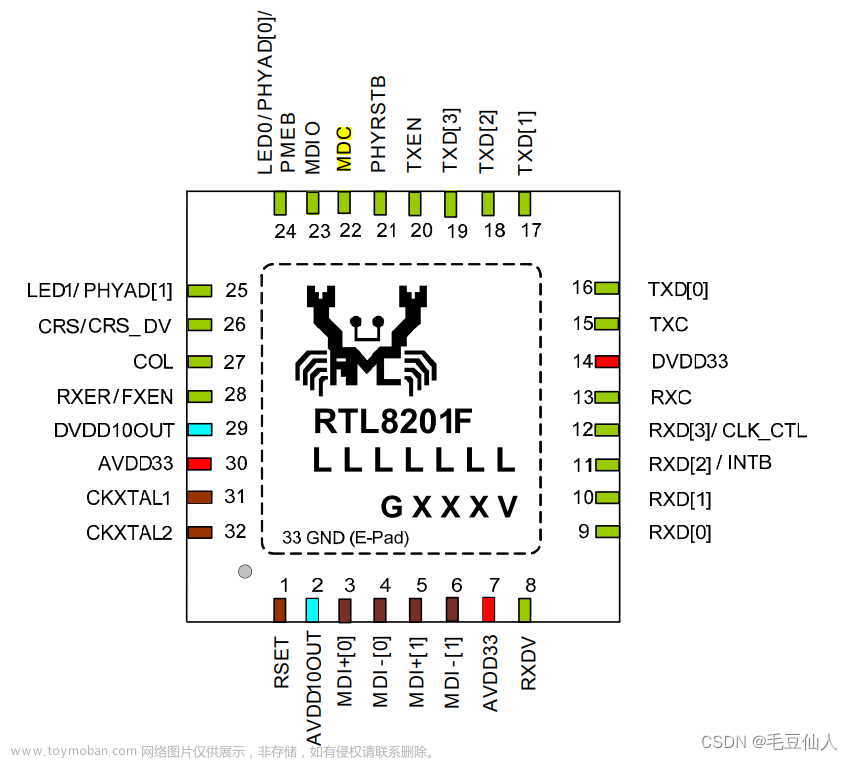

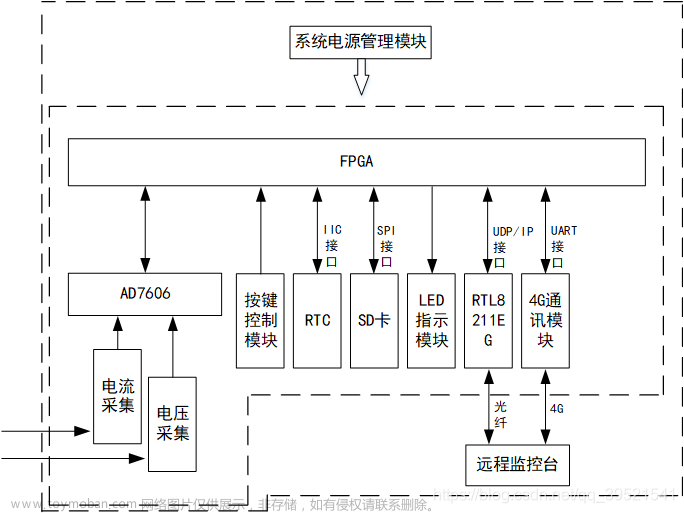

笔者最近在项目中需要使用到ZYNQ中PL端做以太网UDP传输并且需要支持100M/1000M自适应切换。使用的PHY型号为RTL8211。以下分享的主要为利用已有的1000M协议栈修改为100M并且实现二者自适应切换,IP核主要实现以下功能

1、实现100M/1000M自适应

2、回环测试

PS:完整的IP核文件下载地址:https://download.csdn.net/download/qq_24025329/87019436

1、软硬件环境和前置条件

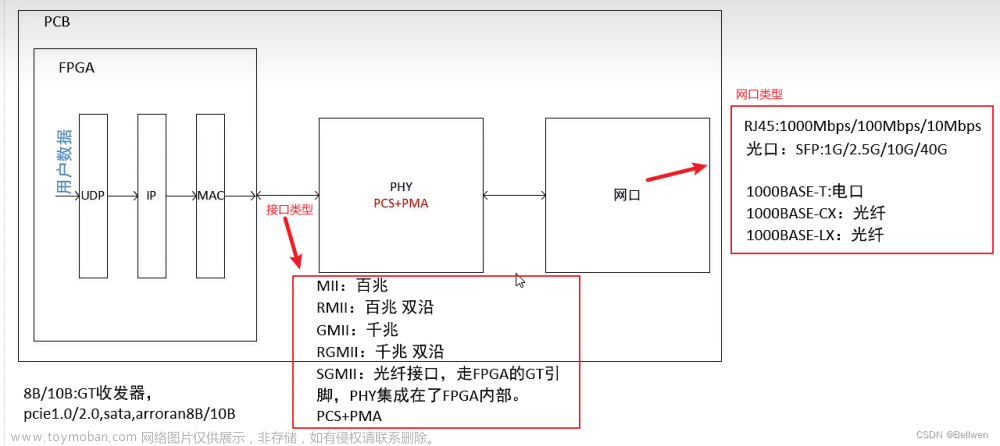

笔者采用的接口是RGMII接口,即100M模式下单边沿采样,时钟频率为25M。在1000M模式下使用双边沿采样,时钟频率为125M。所以在千兆模式下需要使用原语对数据采样,这里就不过多赘述了,这里默认已经拥有了可以实现1000M通讯的协议栈了。

2、实现步骤

第一步:千兆-百兆接收数据转换模块

这里笔者偷了个懒,既然已经有了千兆模式下读取的数据,那么我们只需要根据千兆与百兆之间的采样模式进行转换就可以读出来正确的数据了。具体思想如下

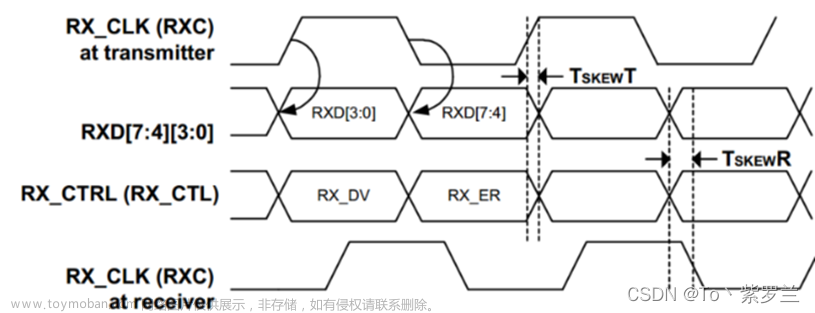

1、千兆为双边沿采样,百兆为单边沿采样。所以在千兆模式RGMII转换为GMII接口下跑百兆的速度读出来的8bit数据中高四位=低四位的。所以我们将读出来的数据只保留四位即可。下图为千兆模式下的采样

2、时钟采用PHY提供的时钟,即百兆模式下25M千兆模式下为125M即可。具体实现代码如下

`timescale 1ns / 1ps

module eth_speed(

input Rst_n, //系统复位

//以太网GMII接口

input gmii_rx_clk , //GMII接收时钟

input gmii_rx_dv , //GMII接收数据有效信号

input [7:0] gmii_rxd , //GMII接收数据

//速度转换后以太网GMII接口

output gmii_rx_clk_s , //GMII接收时钟

output gmii_rx_dv_s , //GMII接收数据有效信号

output reg[7:0] gmii_rxd_s //GMII接收数据

);

//==========参数定义=============//

parameter SPEED = 1000;//1000Mbps

//==========寄存器定义===========//

reg out_clk; //输出时钟

reg count_s; //二分数据计数

reg data0_en;

reg data1_en; //数据有效位

//==========组合逻辑运算=============//

assign gmii_rx_clk_s = out_clk;//输出时钟二分频

assign gmii_rx_dv_s = data0_en && data1_en;//接收数据有效

//==========时序逻辑============//

//输入时钟二分频

always @(posedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

out_clk <= 1'd0;

else

out_clk <= ~out_clk;

//二分数据计数

//第一个数据来临后的第一个下降沿=1

//

always @(negedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

count_s <= 1'd0;

else if(!gmii_rx_dv)//数据无效 清零

count_s <= 1'd0;

else

count_s = ~count_s;//反转

//采集数据1 下降沿采集数据

always @(negedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

gmii_rxd_s[3:0] <= 4'd0;

else if(gmii_rx_dv && (!count_s))//接收数据有效并且二分频时钟位低电平

gmii_rxd_s[3:0] <= gmii_rxd[3:0];

//采集数据2 下降沿采集数据

always @(negedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

gmii_rxd_s[7:4] <= 4'd0;

else if(gmii_rx_dv && (count_s))//接收数据有效并且二分频时钟位低电平

gmii_rxd_s[7:4] <= gmii_rxd[3:0];

//采集数据1有效位

always @(posedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

data0_en <= 1'd0;

else if(!count_s) //第一个数据采样的周期

if(gmii_rx_dv) //有效

data0_en <= 1'd1;

else

data0_en <= 1'd0;

else

data0_en <= data0_en;

//采集数据2有效位

always @(posedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

data1_en <= 1'd0;

else if(count_s) //第二个数据采样的周期

if(gmii_rx_dv) //有效

data1_en <= 1'd1;

else

data1_en <= 1'd0;

else

data1_en <= data1_en;

endmodule

第二步:千兆-百兆接收数据转换模块

发送方面就不能偷懒了,只能自己写了一个百兆模式下的发送,代码如下

`timescale 1ns / 1ps

module eth_speed_tx(

input Rst_n,

input gmii_rx_clk, //来自PHY的时钟

//获得数据接口

input [7:0] data_in, //GMII数据

input data_en, //GMII使能

output data_clk, //GMII时钟,用于获取发送数据,是RGMII的1/2

//RGMII接口

output rgmii_txc, //RGMII的时钟

output reg[3:0]rgmii_txd, //RGMII发送的数据

output rgmii_tx_ctl //RGMII发送控制

);

//========寄存器定义===========//

reg rgmii_txc_2_s;//发送时钟的二分频 并滞后90°

reg en_delay;//输入使能延迟

//==========逻辑==============//

assign data_clk = rgmii_txc_2_s;

assign rgmii_tx_ctl = data_en|en_delay;

assign rgmii_txc = gmii_rx_clk;

//==========时序逻辑==========//

//时钟二分频 用于获得数据 并滞后90°

always@(negedge rgmii_txc or negedge Rst_n)

if(!Rst_n)

rgmii_txc_2_s <= 1'd0;

else

rgmii_txc_2_s <= ~rgmii_txc_2_s;

//发送数据赋值

always @(negedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

rgmii_txd <= 4'd0;

else if(data_en && rgmii_txc_2_s)//要发送第一个4bit数据 低位

rgmii_txd <= data_in[3:0];

else if(data_en && (!rgmii_txc_2_s))//要发送第二个4bit数据 高位

rgmii_txd <= data_in[7:4];

else

rgmii_txd <= rgmii_txd;

//使能延迟

always @(negedge gmii_rx_clk or negedge Rst_n)

if(!Rst_n)

en_delay <= 1'd0;

else if(data_en && (!rgmii_txc_2_s))

en_delay <= 1'd1;

else

en_delay <= 1'd0;

endmodule

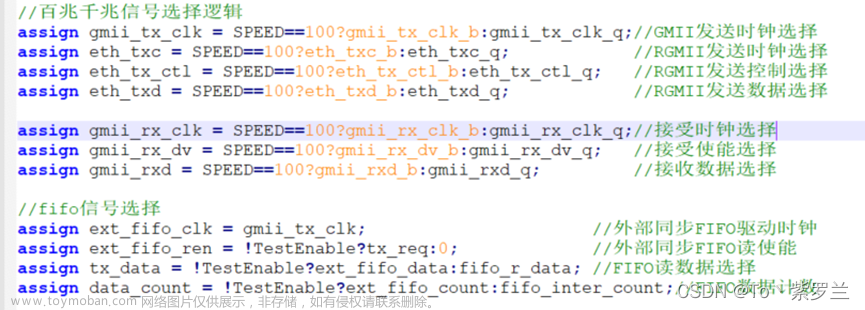

第三步:百兆千兆切换逻辑

百兆和千兆模式下切换本质上就是切换RGMII的接口信号源,具体的逻辑较为简单如图所示

其中SPEED为选择开关,该值可以是定义的参数,也可以当作接口有外部提供。文章来源:https://www.toymoban.com/news/detail-810074.html

最后

该IP核是笔者在项目中解决自己的问题所编写,水平有限如有疏漏敬请指正。文章来源地址https://www.toymoban.com/news/detail-810074.html

到了这里,关于FPGA实现千兆/百兆自适应以太网UDP传输的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!