一、以太网简介

之前提了个引子,接下来我会分享一下基于FPGA的百兆以太网通信学习过程。第一部分是对于以太网PHY芯片的配置和状态读取。

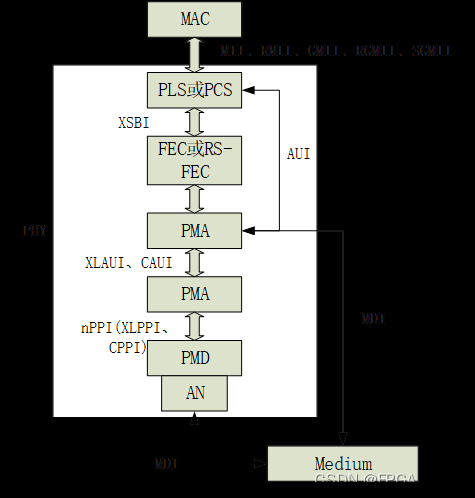

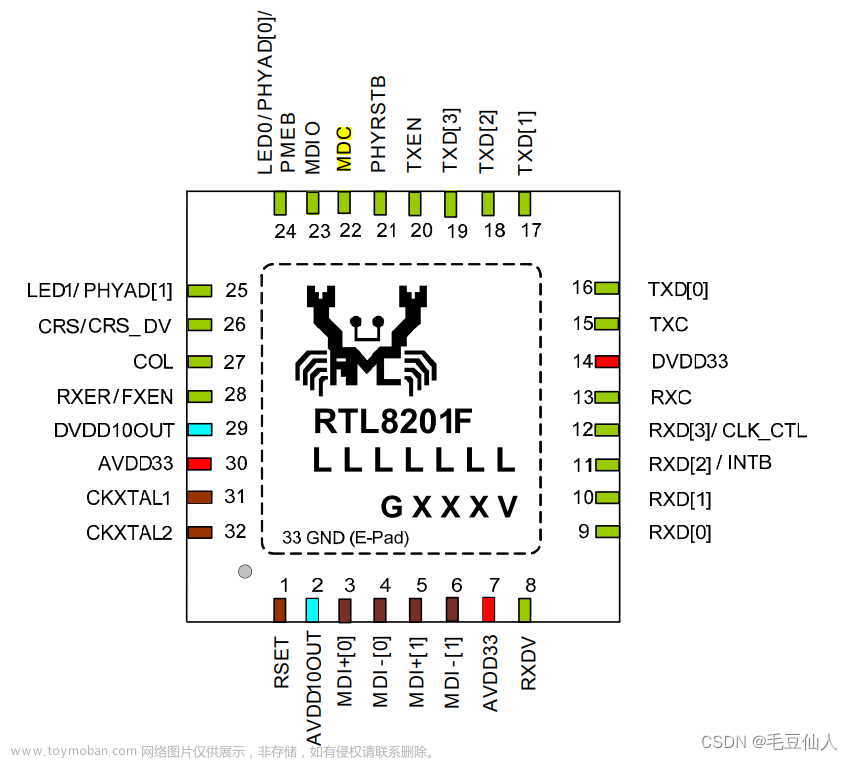

一般来说,FPGA以太网通信是需要外接的PHY芯片的,目前的很多FPGA出厂的底板上已经焊好了PHY芯片,所以这一点是比较方便的。PHY芯片的内部有着很复杂的逻辑和构造,我不懂,这里也不说了,感兴趣的兄弟自己查。

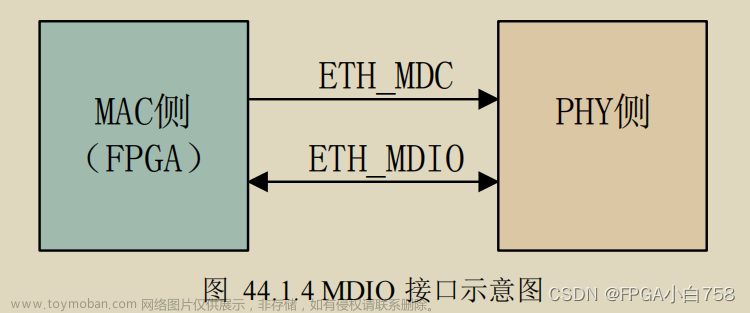

以太网通信需要网线,FPGA以太网通信实际上是FPGA和PHY芯片通信,符合一定的时序和协议,PHY芯片将数据传出和上位机通信。下面给出RTL8201FPHY芯片的管脚图

这里的引脚很多,我们目前只关注两个,MDIO和MDC,这两个是配置引脚,用于配置PHY芯片的寄存器,类似于前面说的摄像头,同时也可以读取其中寄存器的数据。

将FPGA的网口和上位机(如PC)连接后,FPGA的PHY芯片会和上位机进行协商最后形成一个通信速率。假如PHY只支持最高100Mbps通信,而另一端是千兆网口,那么协商速率就是100Mbps。总之会以比较慢的那一段作为标准。当然也可以通过修改寄存器的数据来调整通信速率。比如协商结果是100Mbps,可以改为10Mbps。常用的速率就是100和1000Mbps。

二、实验目标

PHY芯片内部有两个比较重要的数值,第一个是协商的结果,第二个是连接的状态,下面就展开实验读取PHY芯片内部这两个数据。

三、接口分析

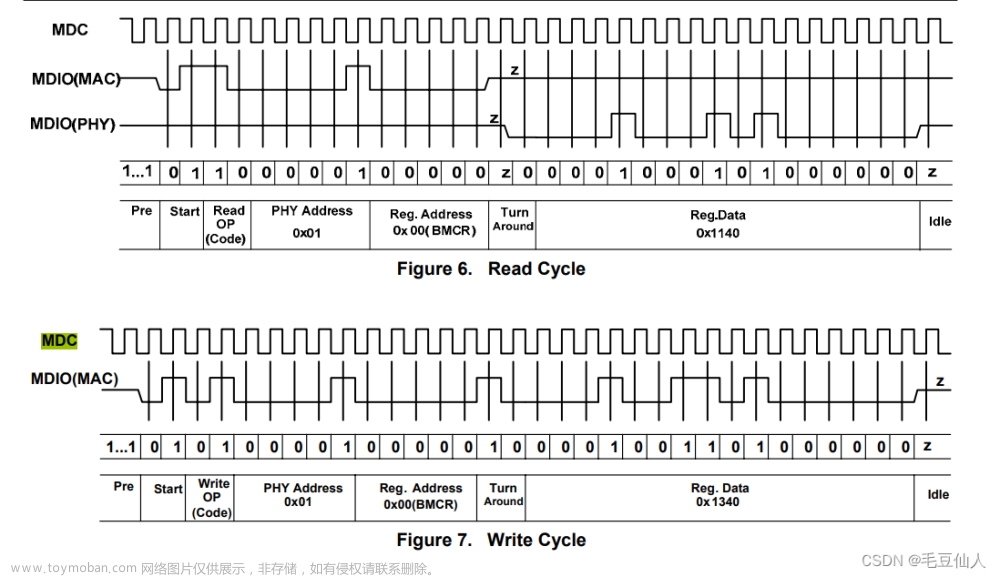

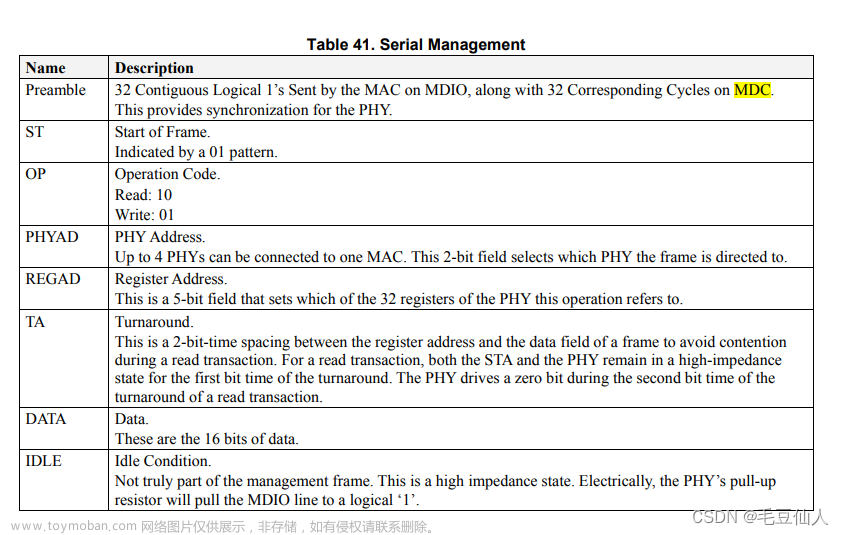

上面提到的MDC和MDIO,MDC是配置的时钟,可以看做IIC里的SCL,MDIO是双向端口,用于传输数据。结构上MDIO和IIC很像。下面是时序图

时序上看和SPI很像,MDIO在每一个MDC的上升沿传输数据,下降沿发生数据转换。上图中可以看出协议的格式,如下图所示

先发32位的前导码preamble,全为1。接着是开始字段,2'b01。操作码,两位,根据是要写还是要读区分。PHY地址(这里需要解释一下,这个好像只是在连接多个PHY芯片的时候才有,用于区分不同的PHY芯片,如果只有一个,默认5'b0,以上是我个人分析,我也不太懂,我查看的教程都说在原理图上可以看出来,但是也没具体说怎么看)。接着是寄存器地址,在手册上查看。TA转换字段,这个我不太懂,就按照手册上写的,如果是读的话就是2'bz0,写的话就是2'b10,最后是十六位数据,最后又回到初始状态。

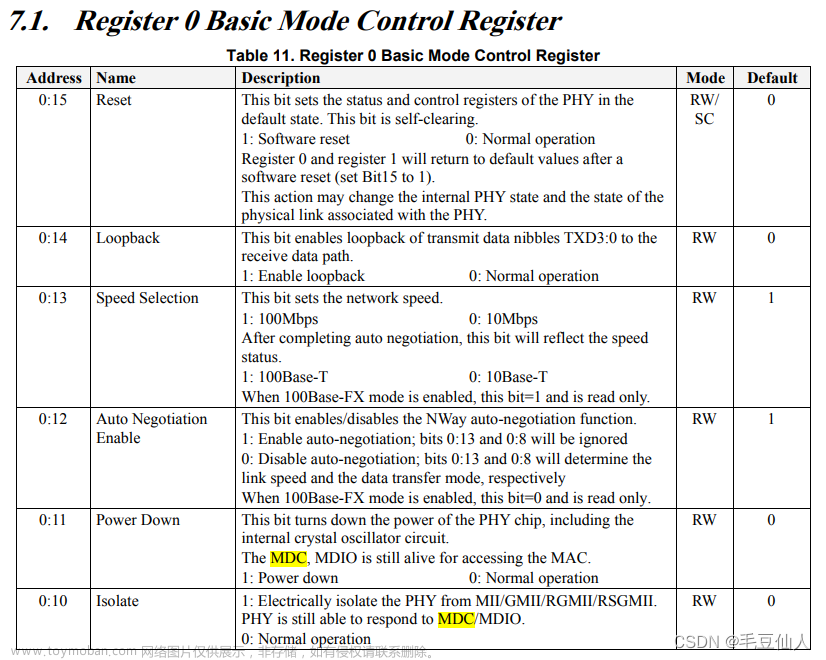

协商结果在第一个寄存器里面

第13位的speed就是协商结果。

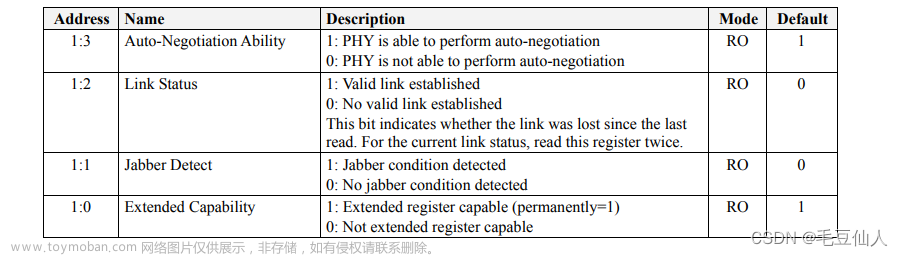

连接状态在第二个寄存器里面

第二位就是连接状态。

最后一点就是MDIO跑不了太高的频率,这里我用的是50k的MDC。文章来源:https://www.toymoban.com/news/detail-846118.html

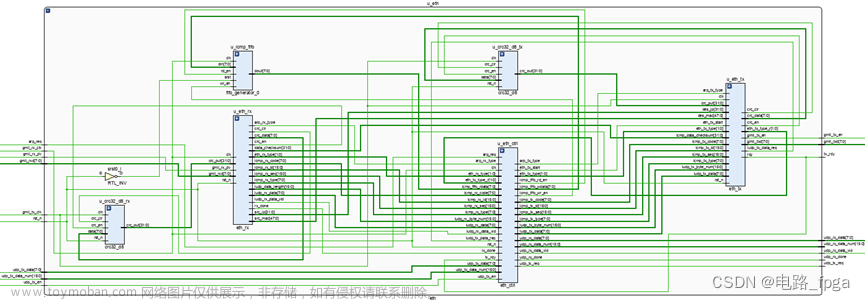

四、代码文章来源地址https://www.toymoban.com/news/detail-846118.html

module mdio_ctrl(

input wire mdc ,

input wire start ,

input wire sys_rst_n ,

input wire [31:0] preamble ,

input wire [1:0] st ,

input wire [1:0] op ,

input wire [4:0] phy_add ,

input wire [4:0] reg_add ,

input wire [1:0] ta ,

output reg speed ,

output reg status ,

output reg ready ,

output wire mdio_en ,

inout wire mdio ,

output wire [7:0] satate

);

reg [7:0] curr_state ;

到了这里,关于基于FPGA的百兆以太网通信(一)——MDIO配置PHY芯片的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!