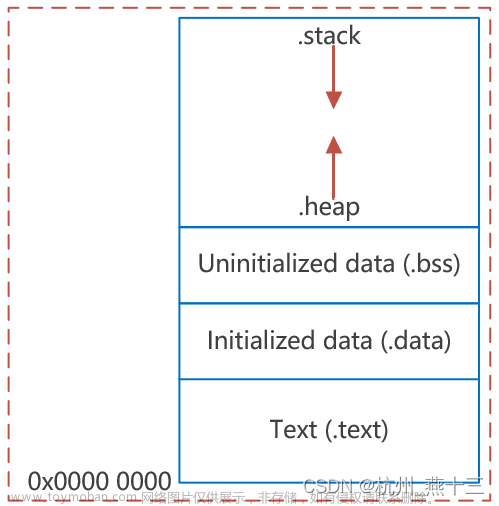

在嵌入式开发中,堆栈是一个很基础,同时也是非常重要的名词,堆栈可分为堆 (Heap) 和栈 (Stack) 。

- 栈(Stack): 一种顺序数据结构,满足后进先出(Last-In / First-Out)的原则,由编译器自动分配和释放。

- 堆(Heap):类似于链表结构,可对任意位置进行操作,通常由程序员手动分配,使用完需及时释放(free),不然容易造成内存泄漏。

1、栈

SP:stack pointer 栈指针,总是指向栈顶。

计算机中的堆栈主要用来保存临时数据、局部变量、存寄存器参数和中断/调用子程序程序的返回地址。

裸机中,SP 指向在系统启动文件中被设置为一个被预留大小的内存块顶部,每次调用函数,把需要的临时变化放入栈中,函数退出后,恢复为调用之前的值。

栈的作用:

- 保存现场

- 传递参数:汇编代码调用C函数时,需传递参数

- 保存临时变量:包括函数的非静态局部变量以及编译器自动生成的其他临时变量

2、栈操作

Cortex-M 中堆栈方向是向低地址方向增长,为满堆栈机制。栈一般放在 .bss 段之后

C语言会自动入栈出栈,所以程序员不需要关心这些(在汇编的时候加入)。汇编语言需要手工处理入栈出栈。

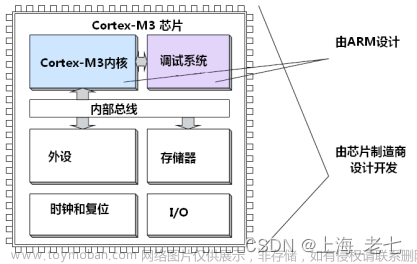

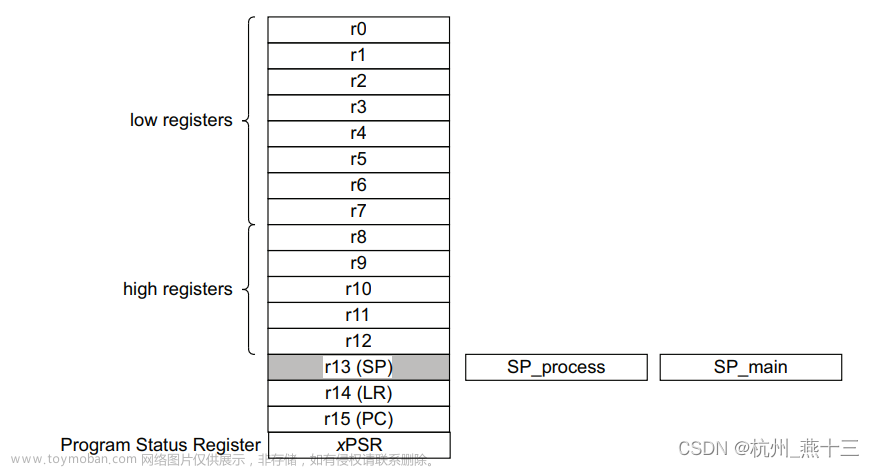

3、Cortex-M中的栈

在 ARM Cortex-M 中 SP 是通用寄存器,为 R13 寄存器

在 Corte-M 中采用双栈设计,分为 MSP 和 PSP。

MSP 和 PSP 的含义是 Main_Stack_Pointer 和 Process_Stack_Pointer,在逻辑地址上他们都是 R13。

权威手册上说的很清楚 PSP 主要是在 Handler 的模式下使用,MSP 主要在线程模式下使用(当然你在线程模式下也可以调用PSP,需要你做特殊的处理)

这意味着同一个逻辑地址,实际上有两个物理寄存器,一个为 MSP,一个为 PSP,在不同的工作模式调用不同的物理寄存器。在任何一个时刻只能使用一个堆栈指针,要么使用 MSP,要么使用 PSP。

-

MSP:主堆栈指针,当程序复位后(开始运行后),一直到第一次任务切换完成前,使用的都是 MSP,即:

main()函数运行时用的是 MSP。 -

PSP:进程堆栈指针,切换任务之后 PendSV 服务程序中有

ORR LR, LR, #0x04这句,意思就是 PendSV 中断返回后使用的 PSP 指针,此时 PSP 已经指向了所运行任务的堆栈,所以返回后就可以就接着该任务继续运行下去了。

裸机中只会用到 MSP,当 main() 函数开始运行前,启动文件会给这个函数分配一个堆栈空间,用于保存 main() 函数运行过程中变量的保存。此时MSP就指向了该堆栈的首地址。

4、MDK中的SP操作流程

以 STM32F103C8T6 为例分析在 MDK 中 SP 相关的运行流程。其中 STM32F103C8T6 内存为 20K(0x5000),地址:0x20000000 ~ 0x20005000。

STM32 中的启动文件 startup_stm32f10x_md.s 文件与 SP 相关部分代码:

; Amount of memory (in bytes) allocated for Stack

; Tailor this value to your application needs

; <h> Stack Configuration

; <o> Stack Size (in Bytes) <0x0-0xFFFFFFFF:8>

; </h>

Stack_Size EQU 0x00000400

AREA STACK, NOINIT, READWRITE, ALIGN=3

Stack_Mem SPACE Stack_Size

__initial_sp

; <h> Heap Configuration

; <o> Heap Size (in Bytes) <0x0-0xFFFFFFFF:8>

; </h>

Heap_Size EQU 0x00000200

AREA HEAP, NOINIT, READWRITE, ALIGN=3

__heap_base

Heap_Mem SPACE Heap_Size

__heap_limit

PRESERVE8

THUMB

; Vector Table Mapped to Address 0 at Reset

AREA RESET, DATA, READONLY

EXPORT __Vectors

EXPORT __Vectors_End

EXPORT __Vectors_Size

__Vectors DCD __initial_sp ; Top of Stack

DCD Reset_Handler ; Reset Handler

DCD NMI_Handler ; NMI Handler

DCD HardFault_Handler ; Hard Fault Handler

DCD MemManage_Handler ; MPU Fault Handler

DCD BusFault_Handler ; Bus Fault Handler

DCD UsageFault_Handler ; Usage Fault Handler

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD 0 ; Reserved

DCD SVC_Handler ; SVCall Handler

DCD DebugMon_Handler ; Debug Monitor Handler

DCD 0 ; Reserved

DCD PendSV_Handler ; PendSV Handler

DCD SysTick_Handler ; SysTick Handler

; External Interrupts

DCD WWDG_IRQHandler ; Window Watchdog

DCD PVD_IRQHandler ; PVD through EXTI Line detect

DCD TAMPER_IRQHandler ; Tamper

DCD RTC_IRQHandler ; RTC

DCD FLASH_IRQHandler ; Flash

DCD RCC_IRQHandler ; RCC

DCD EXTI0_IRQHandler ; EXTI Line 0

DCD EXTI1_IRQHandler ; EXTI Line 1

DCD EXTI2_IRQHandler ; EXTI Line 2

DCD EXTI3_IRQHandler ; EXTI Line 3

DCD EXTI4_IRQHandler ; EXTI Line 4

DCD DMA1_Channel1_IRQHandler ; DMA1 Channel 1

DCD DMA1_Channel2_IRQHandler ; DMA1 Channel 2

DCD DMA1_Channel3_IRQHandler ; DMA1 Channel 3

DCD DMA1_Channel4_IRQHandler ; DMA1 Channel 4

DCD DMA1_Channel5_IRQHandler ; DMA1 Channel 5

DCD DMA1_Channel6_IRQHandler ; DMA1 Channel 6

DCD DMA1_Channel7_IRQHandler ; DMA1 Channel 7

DCD ADC1_2_IRQHandler ; ADC1_2

DCD USB_HP_CAN1_TX_IRQHandler ; USB High Priority or CAN1 TX

DCD USB_LP_CAN1_RX0_IRQHandler ; USB Low Priority or CAN1 RX0

DCD CAN1_RX1_IRQHandler ; CAN1 RX1

DCD CAN1_SCE_IRQHandler ; CAN1 SCE

DCD EXTI9_5_IRQHandler ; EXTI Line 9..5

DCD TIM1_BRK_IRQHandler ; TIM1 Break

DCD TIM1_UP_IRQHandler ; TIM1 Update

DCD TIM1_TRG_COM_IRQHandler ; TIM1 Trigger and Commutation

DCD TIM1_CC_IRQHandler ; TIM1 Capture Compare

DCD TIM2_IRQHandler ; TIM2

DCD TIM3_IRQHandler ; TIM3

DCD TIM4_IRQHandler ; TIM4

DCD I2C1_EV_IRQHandler ; I2C1 Event

DCD I2C1_ER_IRQHandler ; I2C1 Error

DCD I2C2_EV_IRQHandler ; I2C2 Event

DCD I2C2_ER_IRQHandler ; I2C2 Error

DCD SPI1_IRQHandler ; SPI1

DCD SPI2_IRQHandler ; SPI2

DCD USART1_IRQHandler ; USART1

DCD USART2_IRQHandler ; USART2

DCD USART3_IRQHandler ; USART3

DCD EXTI15_10_IRQHandler ; EXTI Line 15..10

DCD RTCAlarm_IRQHandler ; RTC Alarm through EXTI Line

DCD USBWakeUp_IRQHandler ; USB Wakeup from suspend

__Vectors_End

__Vectors_Size EQU __Vectors_End - __Vectors

AREA |.text|, CODE, READONLY

;*******************************************************************************

; User Stack and Heap initialization

;*******************************************************************************

IF :DEF:__MICROLIB

EXPORT __initial_sp

EXPORT __heap_base

EXPORT __heap_limit

ELSE

IMPORT __use_two_region_memory

EXPORT __user_initial_stackheap

__user_initial_stackheap

LDR R0, = Heap_Mem

LDR R1, =(Stack_Mem + USR_Stack_Size)

LDR R2, = (Heap_Mem + Heap_Size)

LDR R3, = Stack_Mem

BX LR

- __initial_sp:指向栈顶,在运行后会赋值给 MSP。Stack_Size:栈大小,当前分配为 0x400。

- __heap_base:堆开始地址;__heap_limit:堆结束地址;Heap_Size:堆大小,当前分配为 0x200。

- __Vectors:中断向量表入口地址,__Vectors_End:中断向量表结束地址;__Vectors_Size:中断向量表大小。

Cortex-M 采用矢量中断模式,中断向量表首地址放的是栈顶地址(__initial_sp)。

- 堆/栈初始化:导出相关变量。MDK 中,是否使用 Micro-LIB,对栈地址影响很大,下面重点讲一下。

5、Micro-Lib的SP差别

1. 使用 Micro-Lib

使用 EXPORT 伪指令分别导出 __initial_sp、__heap_base、__heap_limit,在 __main 中会处理完后跳转到 C 语言的 main() 函数。

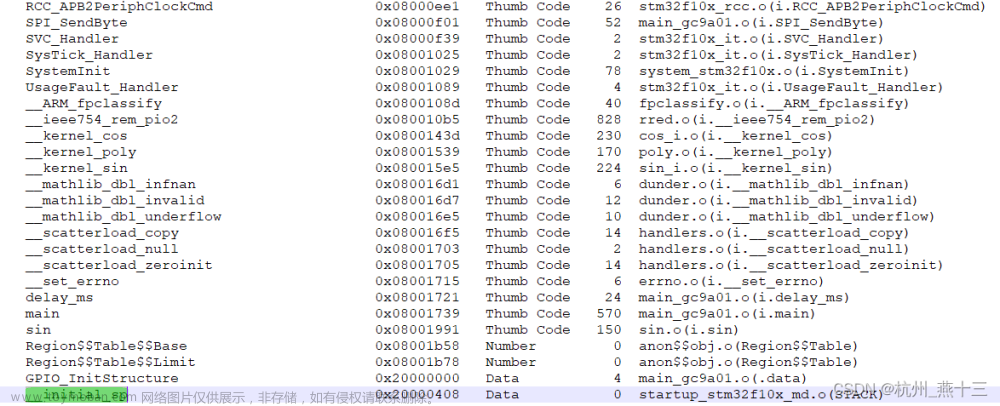

- 查看 MAP 文件可以得到相关的地址信息:

__initial_sp 0x20000408 Data 0 startup_stm32f10x_md.o(STACK)

Execution Region RW_IRAM1 (Exec base: 0x20000000, Load base: 0x08001b78, Size: 0x00000408, Max: 0x00005000, ABSOLUTE)

Exec Addr Load Addr Size Type Attr Idx E Section Name Object

0x20000000 0x08001b78 0x00000004 Data RW 212 .data main_gc9a01.o

0x20000004 0x08001b7c 0x00000004 Data RW 3332 .data mc_w.l(errno.o)

0x20000008 - 0x00000400 Zero RW 186 STACK startup_stm32f10x_md.o

注:查看上面的 MAP 文件,在使用 Micro-LIB 模式下,heap 其实是没有被分配的。

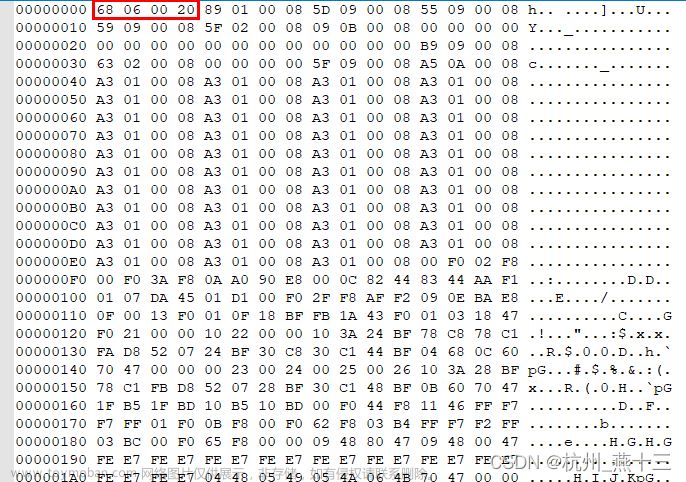

- 通过 SWD 连接芯片,查看 SP 地址

在 startup_stm32f10x_md.s 中 Reset_Handler 中第一句话,SP=0x20000408;进入 main 之后,SP=0x200003F0;进入子函数后:SP=0x200003E8。MSP 与 SP 地址一样。

- 在 main() 中通过代码打印获取以上变量

extern uint32_t __Vectors_End;

extern uint32_t __Vectors;

extern uint32_t __Vectors_Size;

printf("__Vectors: %08x\r\n", (uint32_t)&__Vectors);

printf("__Vectors_End: %08x\r\n", (uint32_t)&__Vectors_End);

printf("__Vectors_Size: %08x\r\n", (uint32_t)&__Vectors_Size);

extern uint32_t __initial_sp;

printf("__initial_sp: %08x\r\n", (uint32_t)&__initial_sp);

运行结果:

__Vectors: 0x08000000

__Vectors_End: 0x080000EC

__Vectors_Size: 0x000000EC # 59 * 4 = 0xec

__initial_sp: 0x20000408

__Vectors 的值与 __initial_sp 的值一致。

2. 未使用 Micro-Lib

-

使用 IMPORT 伪指令导入

__use_two_region_memory,该函数需要用户实现。 -

使用 EXPORT 伪指令导出

__user_initial_stackheap,该函数 startup_stm32f10x_md.s 中已经实现,用于提供编译器的初始化C库函数设置用户程序的堆栈所需要的堆栈信息。文章来源:https://www.toymoban.com/news/detail-691581.html

LDR R0, = Heap_Mem ;堆顶

LDR R1, =(Stack_Mem + Stack_Size) ;栈顶

LDR R2, = (Heap_Mem + Heap_Size) ;堆末地址

LDR R3, = Stack_Mem ;栈首地址

BX LR ;等同于mov pc, lr,跳转并切换指令集,也就是切换到ARM指令集

- 查看 MAP 文件可以得到相关的地址信息:

Execution Region RW_IRAM1 (Exec base: 0x20000000, Load base: 0x08002330, Size: 0x00000668, Max: 0x00005000, ABSOLUTE)

Exec Addr Load Addr Size Type Attr Idx E Section Name Object

0x20000000 0x08002330 0x00000004 Data RW 212 .data main_gc9a01.o

0x20000004 - 0x00000060 Zero RW 3383 .bss c_w.l(libspace.o)

0x20000064 0x08002334 0x00000004 PAD

0x20000068 - 0x00000200 Zero RW 187 HEAP startup_stm32f10x_md.o

0x20000268 - 0x00000400 Zero RW 186 STACK startup_stm32f10x_md.o

- 通过 SWD 连接芯片,查看 SP 地址

在 startup_stm32f10x_md.s 中 Reset_Handler 中第一句话,SP=0x20000668;进入 main 之后,SP=0x20000650;进入子函数后:SP=00x20000648文章来源地址https://www.toymoban.com/news/detail-691581.html

- __Vectors 的值与栈顶地址一致

到了这里,关于ARM Cortex-M 的 SP的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!