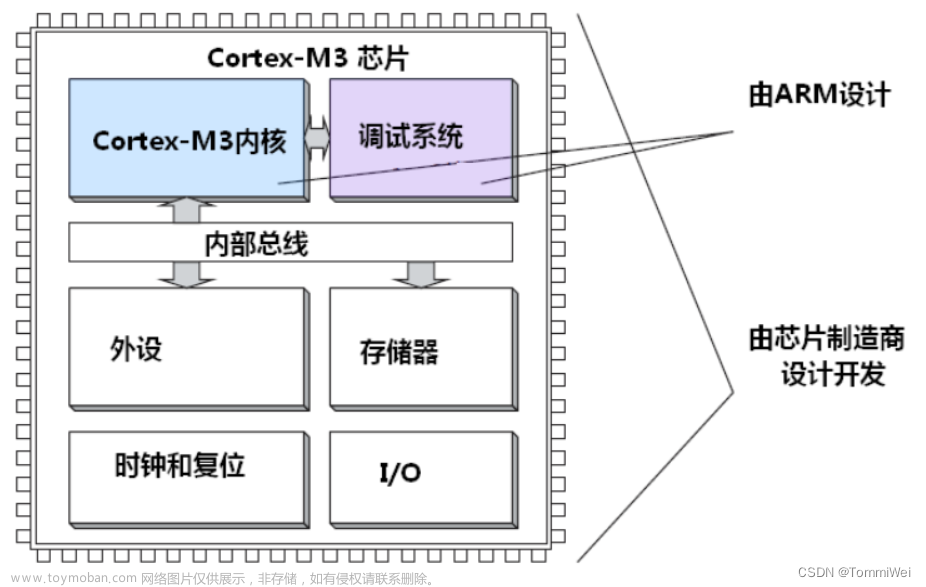

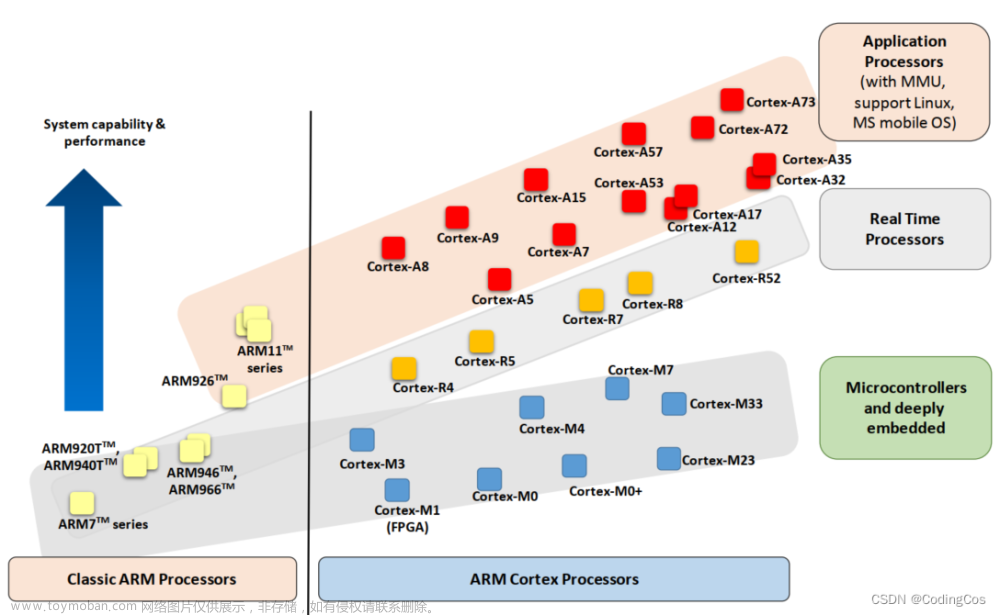

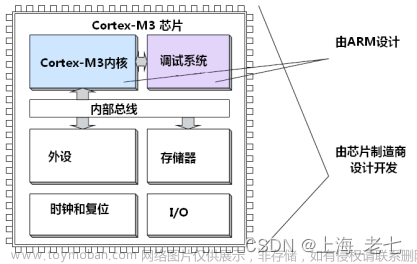

1. cortex-m 处理器的体系架构与指令集

本文仅讨论 cortex-m0/m0+/m3/m4/m7 armv8架构暂不讨论

- cortex-m0/m0+/m1 基于ARMv6-M架构

- cortex-m3基于ARMv7-M架构(ARMv7-M随cortex-m3处理器一起发布)

-

cortex-m4/m7基于ARMv7E-M架构(ARMv7-M随cortex-m4处理器一起发布)

- corte-m处理器都支持Thumb-2指令集(既支持16位指令,也支持32位指令)。

- 上图是ARMv6-M,ARMv7-M,ARMv7E-M所有指令,上图也能看出所支持指令的长度。

- cortex-m1处理器一般用于FPGA,针对FPGA进行了优化

2. cortex-m内核寄存器

2.1 cortex-m0, cortex-m0+寄存器

2.2 cortex-m3, cortex-m4, cortex-m7 寄存器

2.3 PRIMASK、FAULTMASK和BASEPRI寄存器

- PRIMASK:寄存器有1个bit生效,可屏蔽所有 可配置优先级的异常 ,即屏蔽除 Reset(-3), NMI(-2), HardFault(-2) 外的所有中断。

- FAULTMASK:寄存器有1个bit生效,屏蔽除 Reset(-3), NMI(-2) 外的所有中断。

-

BASEPRI:可屏蔽优先级 小于或等于 BASEPRI配置值的中断或异常。BASEPRI位宽是可配置的(微控制器设计厂商可配置,非软件可配置),一般是3bit 或 4bit。

2.4 SP寄存器

SP寄存器在物理实现上有两个,分别是MSP 和 PSP,通过SP这个名字访问的可能是不同的物理存储,当然也可以直接在汇编中使用MSP 和 PSP。

- MSP:Main Stack Pointer(主栈指针),Handler mode(处理异常或中断)使用MSP,Thread mode可以选择使用MSP或PSP(通过CONTROL寄存器选择)

- PSP:Process Stack Pointer(线程栈指针),在Thread mode下可由CONTROL寄存器配置使用PSP.

3. PSR 寄存器

因为支持的指令不同,所以不同处理器的PSR寄存器会略有不同

3.1 cortex-m0, cortex-m0+(ARMv6-M)

3.2 cortex-m3(ARMv7-M)

3.3 cortex-m4,cortex-m7(ARMv7E-M)

- GE[3:0]:大于或等于标志

- ICI:Interruptible-continuable instruction(中断继续指令),如LDM指令,STM指令均需要多个时钟周期,且是可被中断的, ICI只要作用是记录中断位置。

- IT:用于If-Then指令(IT指令,在此处暂不展开讨论IT指令)。

- T:指示处于ARM状态还是Thumb状态,cortex-m处理器只支持Thumb状态,所以此位一直为1。

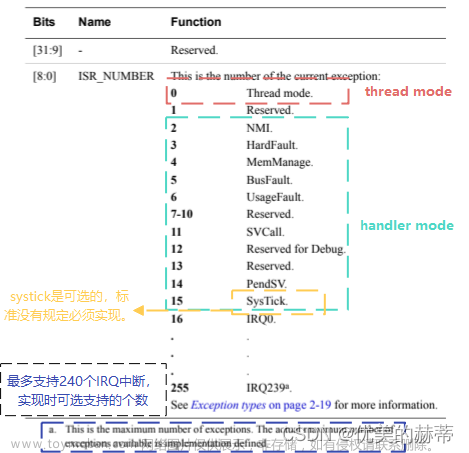

3.4 ISR_NUMBER

-

cortex-m0/m0+的ISR_NUMBER

-

cortex-m3/m4/m7的ISR_NUMBER

-

总结

-

cortex-m3/m4/m7相比cortex-m0/m0+ 增加了如下异常

- MemManage

- BusFault

- UsageFault

- Reserved for Debug

- cortex-m3/m4/m7相比cortex-m0/m0+ IRQ中断数量由32个扩展到了240个

- systick在cortex-m0/m0+ 中是可选实现的,systick 在 cortex-m3/m4/m7中是必须实现的。

-

cortex-m3/m4/m7相比cortex-m0/m0+ 增加了如下异常

4. cortex-m处理器模式与特权级

4.1 cortex-m处理器特权级

cortex-m处理器分为两个特权级:

-

Unprivileged(非特权级)

- 不能使用MRS,MSR,CPS(开关中断) 指令。

- 不能访问systick、NVIC、SCB等

- 对MPU保护的资源访问受限

注:cortex-m0不支持非特权模式(CONTROL没有对应的配置位)。cortex-m0+ 可选的支持非特权模式。cortex-m3/m4/m7强制支持非特权模式。

-

Privileged(特权):

- 所有指令,所有资源均可访问。

4.2 cortex-m0/m0+处理器寄存器访问的特权级

- cortex-m0只支持特权级(不支持非特权级),所有的寄存器都只能在特权级下访问。

- cortex-m0+可已选择支持特权级,也可以选择不支持特权级。

<<DUI0662B_cortex_m0p_r0p1_dgug>> 文档中并没有对各个寄存器中访问的特权级进行描述,欢迎大家补充,或后续我找一下其他资料或实测一下再补充。

4.3 cortex-m3/m4/m7处理器寄存器访问的特权级

- cortex-m3/m4 存器访问的特权级

- cortex-m7 存器访问的特权级

- 由上面两个表可以看出cortex-m7 和 cortext-m3/m4 仅在 MSP的访问权限上存在区别。

4.4 cortex-m处理器模式

-

Thread mode:线程模式(没有进行中断处理)

- 可配置特权模式或者非特权模式 ,CONTROL寄存器配置,。

- 可配置使用MSP或者PSP,CONTROL寄存器配置。

注:在Thread mode下,cortex-m0只支持特权模式(CONTROL寄存器没有相关的配置位),cortex-m0+可选支持非特权模式,cortex-m3/m4/m7既支持特权模式,也支持非特权模式。

-

Handler mode:处理模式

- 一定处于特权模式

- 使用MSP

4.5 cortex-m处理器模式和特权级切换简析

- 下表是寄存器的初始值,通过寄存器的初始值我们可以得出很多结论

4.5.1 CONTROL寄存器的初始值

CONTROL寄存器的初始值为全0,我们可以得出如下结论:

- 针对cortex-m0或cortex-m0+(不支持非特权级) ,表征在初始状态下使用MSP

- 针对cortex-m0+(支持非特权级)/m4/m7,表征在初始状态下使用MSP且处于特权模式。

cortex-m4/m7在 CONTROL寄存器中增加了FPCA位用于指示中断发生时上下文中有没有浮点运算,用于指示中断发生时的硬件压栈,这与cortex-m的异常处理有关,在此暂不展开,后续会专门写一篇文章来分析cortex-m的异常处理。

4.5.2 PSR寄存器的初始值

- PSR寄存器的初始为0x01000000, 即T位为1表示处于thumb状态(cortex-m只支持Thumb状态),ISR_NUMBER 为零表示处于Thread mode

4.5.3 PRIMASK,FAULTMASK,BASEPRI寄存器的初始值

PRIMASK,FAULTMASK,BASEPRI寄存器的初始值都为0,便是不屏蔽任何中断。

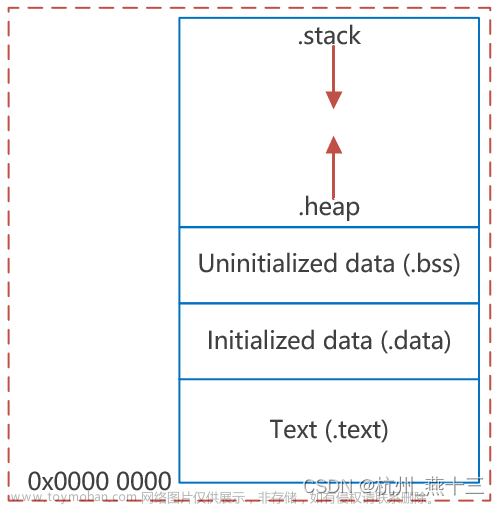

4.5.4 MSP PSP PC寄存器的初始值

初始状态下栈指针使用MSP , 不关心PSP的初始值,MSP PC寄存器的初始值比较特殊,上电或复位后,硬件会将向量表中的第一个字放入MSP中,将向量表中的第二个字放入PC中,又因为复位状态下VTOR 寄存器的初始值为0,所以硬件会到0地址处找向量表,软件要保证0地址出有向量表。

4.5.5 LR寄存器的初始值

LR寄存器的初始值是0xFFFFFFFF,这是一个非法值,函数调用不会在这里返回。文章来源:https://www.toymoban.com/news/detail-794330.html

4.5.6 总结

结合通过上述描述,我画了一张图描述状态和特权级的切换,比较好理解,便不过多赘述。 文章来源地址https://www.toymoban.com/news/detail-794330.html

文章来源地址https://www.toymoban.com/news/detail-794330.html

到了这里,关于arm cortex-m 架构简述的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!