在本篇文章中,我们将讨论HMC7044调试和FPGA开发的相关内容。我们将介绍如何使用HMC7044高性能时钟管理器,并提供一些示例源代码来帮助您开始使用该设备。

HMC7044概述

HMC7044是一款高性能时钟管理器,可用于FPGA和其他数字系统中的时钟分配和时钟生成。它提供了多个时钟输出通道,可以生成高精度的时钟信号,并支持各种时钟分频和分配方案。使用HMC7044可以实现精确的时钟同步和时钟分配,是许多FPGA系统中的关键组件。

HMC7044的调试

在开始使用HMC7044之前,首先需要进行调试和配置。以下是一些调试HMC7044时钟管理器的步骤:

-

连接硬件:将HMC7044与您的FPGA开发板或目标系统进行连接。确保所有必要的电源和信号线连接正确。

-

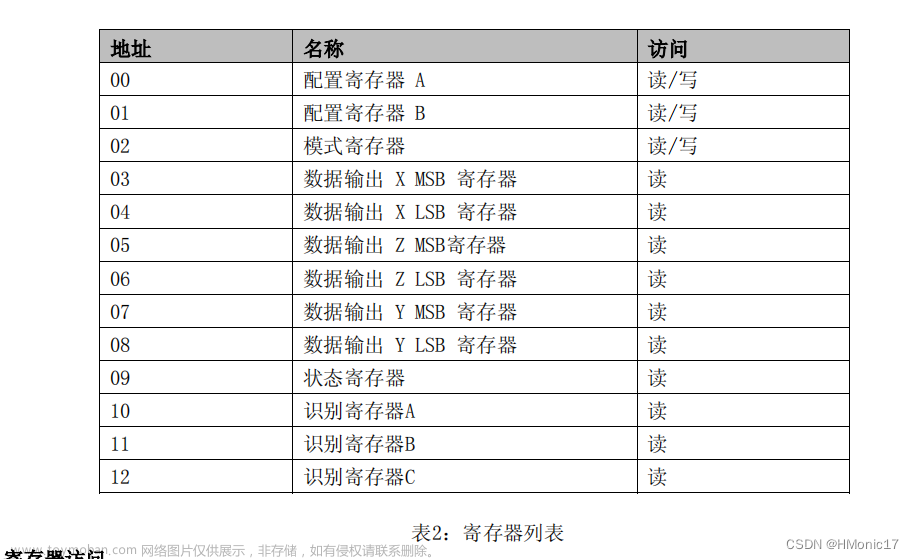

配置寄存器:HMC7044通过I2C接口进行配置。您需要通过I2C总线与HMC7044进行通信,并设置适当的寄存器值以配置时钟输出通道、分频比和其他参数。您可以根据您的系统需求参考HMC7044的数据手册来了解可用的寄存器和配置选项。

-

初始化时钟:在配置HMC7044之后,您需要初始化时钟输出通道。这包括选择合适的时钟源、分频比和延迟参数。根据您的应用需求,您可以选择不同的时钟分配方案,例如使用PLL生成特定频率的时钟信号,或者通过分频器生成较低频率的时钟信号。

-

验证时钟输出:完成初始化后,您可以验证HMC7044的时钟输出是否按预期工作。使用示波器或逻辑分析仪来检测时钟信号,并确保其频率和相位与您的期望一致。文章来源:https://www.toymoban.com/news/detail-757917.html

下面是一个基本的C代码示例,演示如何通过I2C总线与HMC7044进行通信和配置:文章来源地址https://www.toymoban.com/news/detail-757917.html

到了这里,关于HMC7044调试指南与FPGA开发的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!