一、架构简述

串行信号经过传输媒介时,必然伴随着衰减或者扭曲。为了减少信号衰减带来的串行误码率,并且兼顾功耗与性能,GT收发器提供了两种信号改善方法:一种是LPM模式(low-power mode),另一种是DFE模式(判决反馈均衡器Decision Feedback Equalizer)。

DFE模式是一种离散时间的自适应高通滤波器(DFE实现了一种非线性均衡器),相比较线性均衡器,提供了更好的滤波器参数,能够提供更佳的信号增益补偿。后面会大致介绍一下线性均衡器与DFE均衡器的架构与实现方式。

LPM模式架构:

GTX DFE模式架构:

GTH DFE模式架构:

下面对架构图中各模块进行解析。

1.1、AGC 模块

图中,AGC(自动增益控制),一般用于信号接收强度的检测,并自动控制信号的增益。AGC一般分为前馈式和反馈式两种结构。

前馈式电路:检测电路输入信号的幅度大小,调整增益的大小。

反馈式电路:检测电路输出信号的幅度大小,调整增益的大小。

AGC电路能够使收发器接收输入信号的幅度在特定范围内变化,保证接收弱信号时可以对其进行增益,不至于信号太小而无法工作。

1.2 均衡器

在分析赛灵思高速收发器的均衡器之前,我们先了解一下什么是均衡器。

均衡是对信道特性的均衡,指的是形成与信道完全相反的传输特性,以抵消或者减少信道造成的码间干扰,从而避免信号的失真。均衡器主要分为线性均衡器与非线性均衡器。线性均衡器与非线性均衡器的主要区别,在于均衡器的输出是否反馈作用于均衡器,若经过反馈则是非线性均衡器,反之则是线性均衡器。

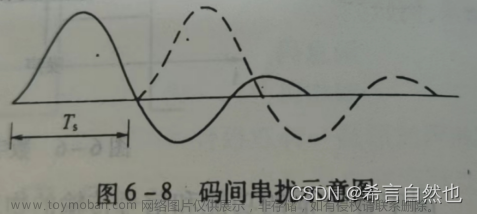

码间干扰(ISI)一般是由于系统的传输特性不理想,导致前后码元的波形畸变、展宽、使前面的波形出现很长的拖尾,从而对当前码元造成干扰。

图中实线部分为当前码元示意图,虚线部分为拖尾后的码元示意图。可见当前码元与拖尾后码元相互影响、叠加,可能会影响最终接收到的信号。

举例如下:假设发送源发送的波形为标准正弦波,接收端接收正弦波。由于信号存在拖尾现象,当前时刻的实际接收的波形幅值是之前波形信号的拖尾与理想正弦波形的叠加。

1.2.1、linear EQ与CTLE

线性均衡器(linear equalizer,linear EQ),连续时间线性均衡器(CTLE)。根据架构图可以看到,LPM模式和GTH的DFE模式使用的是同一种均衡器linear EQ,GTX使用的是另一种均衡器CTLE。二者的配置寄存器不同。下面介绍一下均衡器。

线性均衡器常用的结构有横向均衡器与格型均衡器,算法有匹配滤波(MF)、迫零(ZF)算法和最小均方误差(MMSE)算法等等。此处不详细探究这些算法,只需要了解,线性均衡器往往伴随着噪声放大的问题。

线性均衡器中,最常用的是线性横向均衡器,由若干个抽头延迟组成,延时间隔等于码元间隔。横向均衡器的架构如下图所示,其核心是一个横向滤波器,利用滤波器的架构使接收信号尽可能不失真。

其中图(a)为横向滤波器的架构,具有2N+1个抽头,需要合理的选择参数C的数值。图(b)为等待被均衡器(滤波器)处理的接收信号。注意此时假设接收信号无噪声,只存在码间串扰。图(c)为均衡器(滤波器)处理后的信号。可以从图中看到,经过处理后的信号得到一定程度的还原 。

1.2.2、 DFE

判决反馈均衡器(Decision Feedback Equalier,DFE均衡器)是非线性均衡器中常用的一种。由于线性均衡器会放大噪声,并且线性均衡的效果存在上限,因此需要进一步的均衡机制。赛灵思采用了DFE均衡机制。

前面讲到信号的在信道中传输存在拖尾现象,会影响到下一个码元。那么如果将上一个码元对当前码元的影响进行消减,那么就可以将码元干扰降低甚至消除。那么如何实现呢?

如果能够准确的判断第一个码元的话,将结果延迟反馈到输入信号处,并适当减掉部分量,则第二个码元就更容易判断准确。这也是判决反馈均衡器(Decision-Feedback Equalier)的字面含义。

如上图,为DFE均衡器的简易结构图。实现时,连续接收信号,通过时钟控制的采样器,得到采样数据Dout,经过Td的延迟,通过权重h1和h2与输入数据相加。合适的延迟时间td和权重h1,h2就能保证将输入数据的码间干扰降低或完全消除。

1.3、SIPO

Serial in parallel out,串并转换,将串行数据转换成并行数据。

二、如何选择LPM模式和DFE模式

LPM模式推荐使用在线速率11.2Gb/s以下、媒介的损耗在12dB以下的短路径应用。

DFE模式推荐使用在媒介损耗在8dB以上的中长路径的应用中。当存在串行串扰时,DFE模式是最佳选择。

在8b/10b编码或者不采用数据加扰器(data scrampler)的应用中,采用DFE模式时要求进入的数据是随机的。

当然,对于不同的线路板,线路的损耗是不同的,使用LPM还是使用DFE模式,基于理论计算往往不能完全符合实际,实际工程应用中,可以通过实际测试来确定到底使用哪种模式。

此处额外说一下8b10b编码和数据加扰器。

8b10b编码:

8bits数据8’bHGFEDCBA,拆分成低5bits的5’bEDCBA(设其十进制数值为X)和高3bits的3’bHGF(设其十进制数值为Y),则该8bits数据可以表示成D.X.Y。如果该数据是控制字符,则表示成K.X.Y。8B/10B编码中将K28.1、K28.5和K28.7作为K码的控制字符,称为“comma”。在任意数据组合中,comma只作为控制字符出现。

编码时,将低5bits的5’bEDCBA编码成6bits的6’b iedvba;将高3bits的3’bHGF编码成4bits的4’bjhgf。如下图。8bit数据有256种,加上12种控制字符,总共有268种。10bit数据有1024种,可以从中选择出一部分表示8bit数据,所选的码型中0和1的个数应尽量相等。

使用运行不一致性来描述编码数据中0出现的位数与1出现的位数的差值(该差值仅存3种情况:-2/0/2)。比如数据10’b0100_011000,0出现的次数与1出现的次数的差值为2。

由于数据不停地从发送端向接收端传输,前面所有已发送数据的不一致性累积的状态称为运行不一致性(Runing Disparity,RD)。RD仅会出现1和-1两个状态,分别代表位1出现的次数比位0出现的次数多或者少。标准的编码映射表格与RD有关。

由此可见,8b10b编码的DC性较好,高低电平出现的概率大致相等。

数据加扰器(data scrampler):

使用固定的算法,将原始数据进行处理,使其在时间、频率上被打散,减少出现连续的0或者连续的1,防止出现频谱峰值。文章来源:https://www.toymoban.com/news/detail-775816.html

因为DFE模式架构实际是一个高通滤波器,当出现连续的0或者连续的1时,即连续的高低电平时,数据被截止,此时就需要在发送端增加一个数据加扰器,接收端增加一个数据解扰器,实现正常的数据传输。文章来源地址https://www.toymoban.com/news/detail-775816.html

到了这里,关于赛灵思7系列FPGA GT收发器中的RX均衡器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!