提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

在一次笔试题中遇到了带时钟抖动(jitter)的建立/保持时间计算的问题,当时对时钟抖动概念不是很清晰,然后没写出来,笔试结束后去网上搜索发现只有时钟抖动的概念,并无相关计算(也可能自己没有找到),然后咨询了一位做数字IC相关的老师,最后算是的到了比较清楚的答案了吧,写一下自己的理解。

可能有叙述错误,欢迎大家评论留言,我一定改!

一、什么时钟抖动和时钟偏移?

这个概念网上一搜一大堆,都解答的比较详细,我这里简要介绍一下吧。

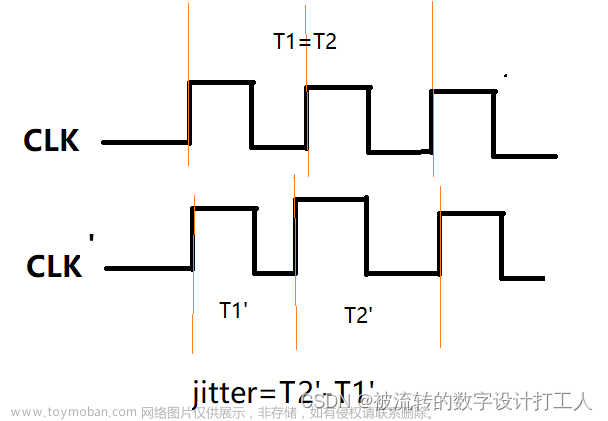

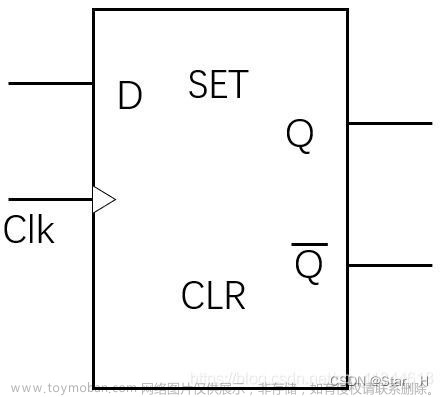

时钟抖动:指的是某一时刻时钟周期会发生短暂性变化(向左或向右偏移),造成时钟周期在不同的周期上可能加长或缩短。它一般发生在时钟发生器内部,和晶振和PLL内部电路有关,与布线无关。是频率上的不确定。

它的计算:jitter=Tmax-Tmin,如下图所示:

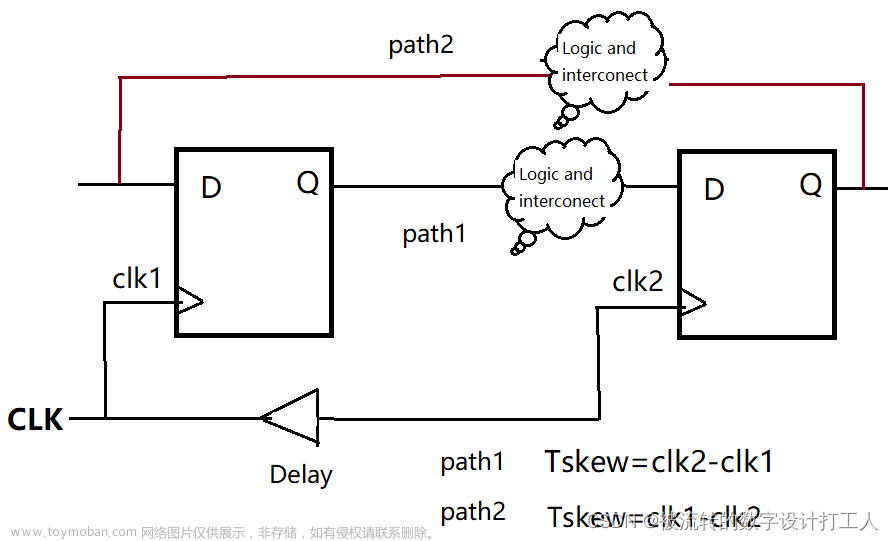

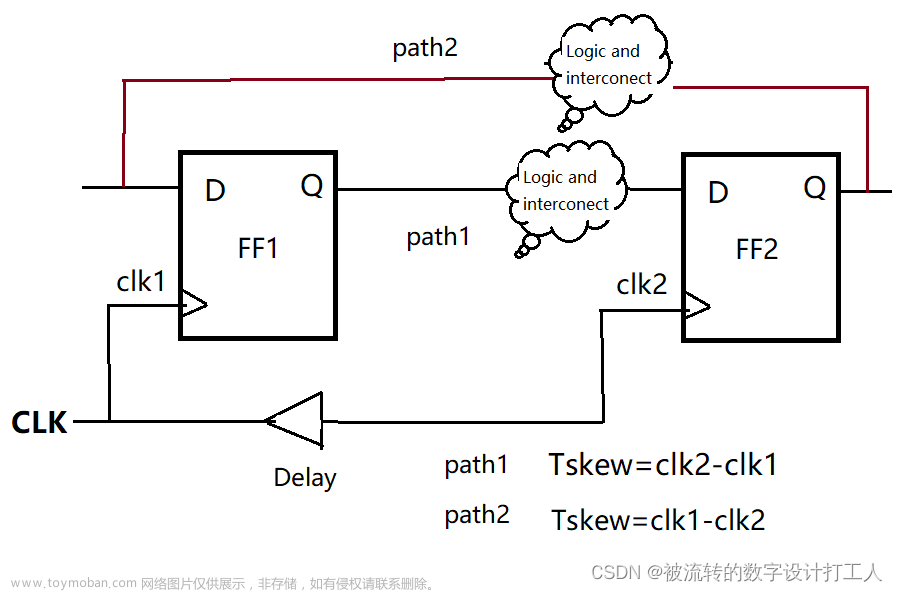

时钟偏移:是指同一时钟由于布线长度不同导致时钟到达不同寄存器的时间不同,存在一定差值。时钟偏移是永远存在的,它的大小和电路布线有关。是相位上的不确定。

它的计算:Tskew=clk2-clk1,

注意这里结果可能是正,也可能是负。正常来说,时钟到达clk1的时间肯定比到达clk2的时间短,但是我们在进行时序分析的时候,看的是源端触发器到目的端触发器之间的时序路径,假如有一条时序路径是从FF2到达FF1(path2),

那么其Tskew=clk1-clk2;

二、包含时钟抖动和时钟偏移的建立/保持时间余量的计算

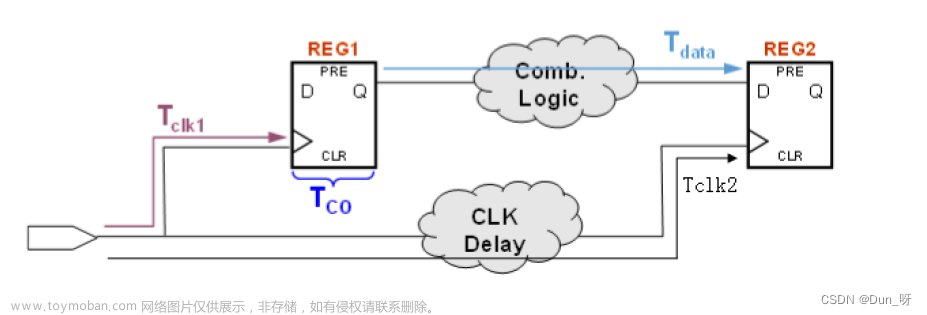

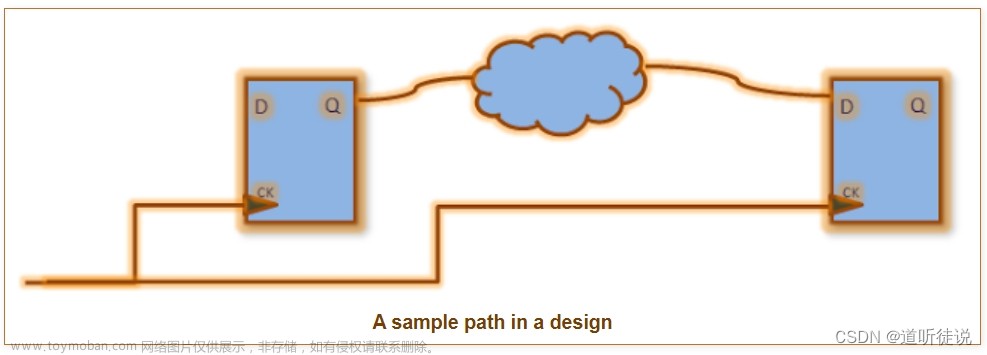

1.带时钟延迟的计算

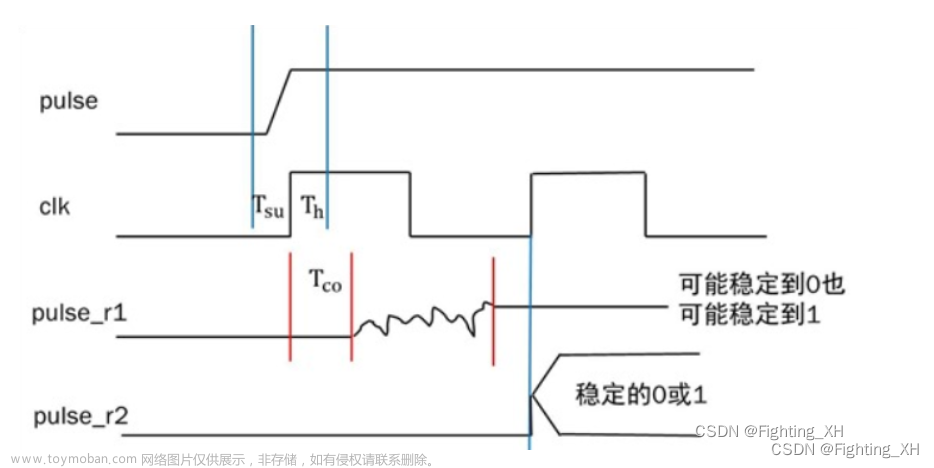

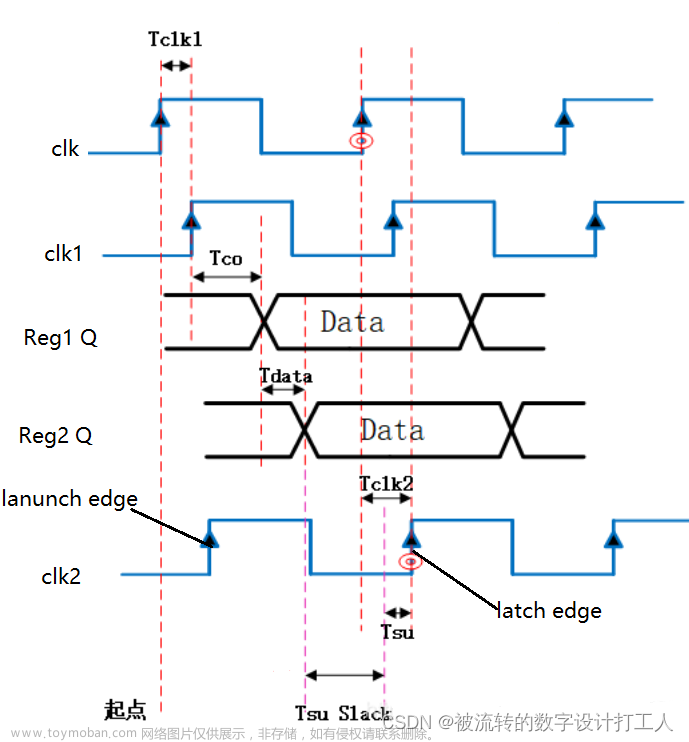

这一点应该是很好理解的,我们从时序图出发,如下图所示:

这里将Reg1 到Reg2的逻辑延迟Tlogic和路径延迟Troutine统称为Tdata;

要求数据到达时间:Trequire=Tclk+Tclk2-Tsu;

实际数据到达时间: Tarrive=Tclk1+Tco+Tdata;

建立时间余量=Trequire-Tarrive=Tclk-Tco-Tdata+Tskew-Tsu;(Tskew=clk2-clk1)

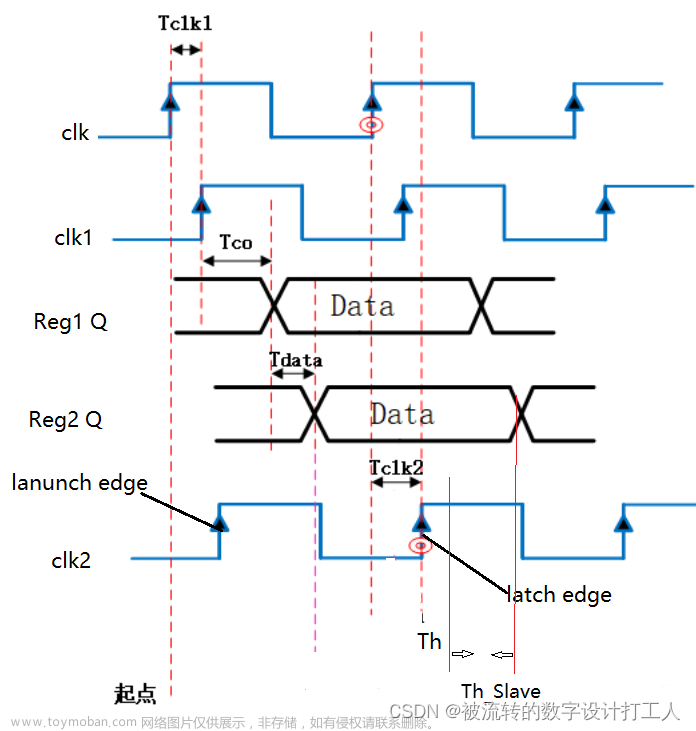

实际数据结束时间:Tclk+Tclk1+Tco+Tdata;

要求数据结束时间 Tclk+tclk2+Th;

保持时间余量 =Tco+Tdata+Tclk1-Tclk2-Th=Tco+Tdata-Tskew+Th;(Tskew=clk2-clk1)

2.带时钟抖动的计算

因为时钟抖动的发生是不确定的,它是在某个时钟周期产生周期的增加或缩小,所以一般也可将时钟抖动称为时钟不确定(Uncertainty).

如本文第一张图片所示,我们可以理解时钟抖动是某一周期时钟上升沿向左或向右偏移,在进行建立/保持时间余量计算的时候,其建立时间/和保持时间的时钟不确定应该分开表示并进行计算。

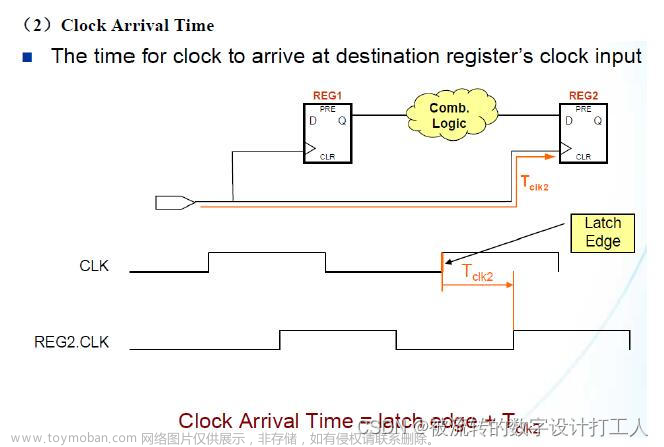

数据到达时间=latch edge +Tclk2=Tclk+Tclk2;

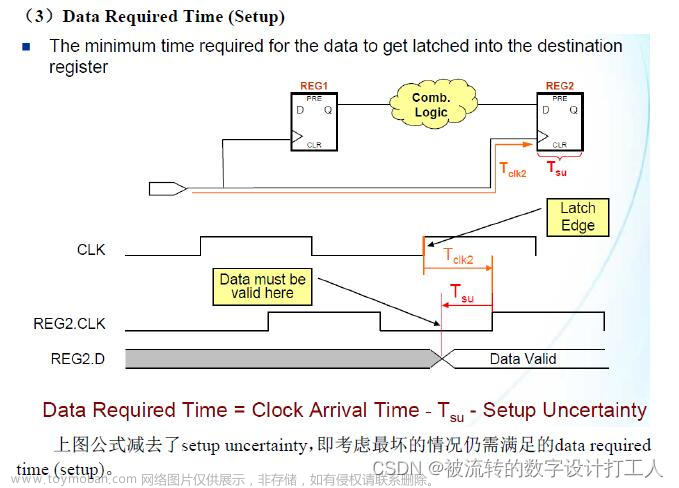

对于建立时间而言:

数据要求到达时间=clock arrival time-Tsu-Set Uncertainty=Tclk+Tclk2-Tsu-Setup Uncertainty;

数据实际到达时间不变:arrive=Tclk1+Tco+Tdata(不变)

建立时间余量=Trequire-Tarrive=Tclk-Tco-Tdata+Tskew-Tsu-Setup Uncertainty;(Tskew=clk2-clk1)

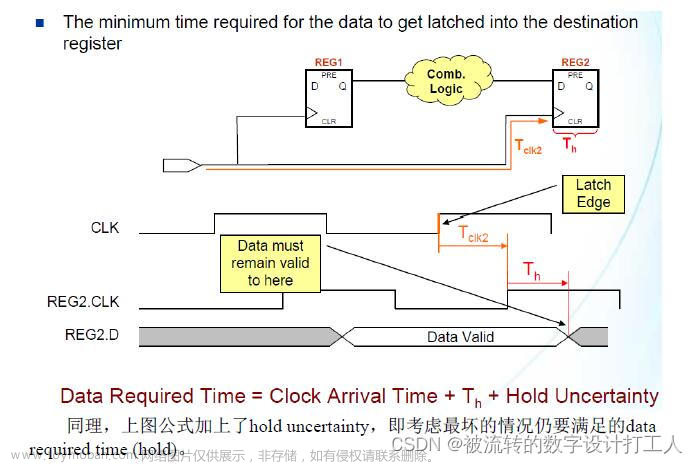

同理,对于保持时间而言:

实际数据结束时间:Tclk+Tclk1+Tco+Tdata(不变)

要求数据结束时间 Tclk+tclk2+Th+Hold Uncertainty;

保持时间余量 =Tco+Tdata+Tclk1-Tclk2-Th=Tco+Tdata-Tskew+Th+Hold Uncertainty;(Tskew=clk2-clk1)

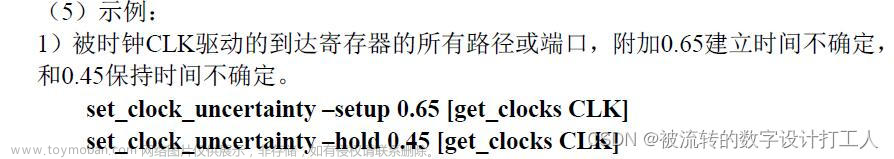

一般情况下,建立/保持时钟不确定性会直接给出的,如下所示:

注意:

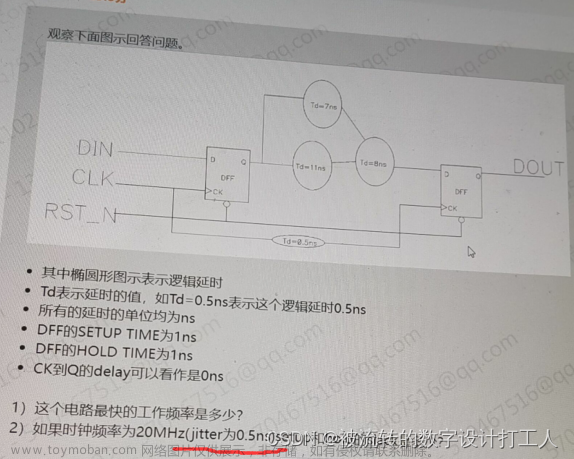

有时候在计算时,题目只会给出一个jitter的值,如下图所示:

这种情况为了结果的准确性,我们在计算建立/保持时间余量的时候就要减去/加上 1/2的jitter。

为什么取1/2呢?

这是因为jitter在计算的时候取的时钟周期的最大值与最小值之间的差值,它有可能是正负偏差的合集,除以二就可以得到相对于中间的那个上升沿(latch edge)的偏差值,这样在进行建立/保持时间余量的计算时相对比较可靠。

但这种情况只能做一个理论的计算,因为在实际工程中正的偏差和负的偏差有可能不是一半,所以比较准确的描述还是应该像上面图片中(5)示例那样分开定义的。文章来源:https://www.toymoban.com/news/detail-791377.html

总结

在进行时钟抖动相关计算时,若题目分别给出建立/保持时间的时钟不确定性,计算建立时间余量就是减去Setup Uncertainty,计算保持时间余量就是加上 Hold Uncertainty;若题目只给了一个jitter的值,那么就可以近似用1/2的jitter去代替Setup Uncertainty和Hold Uncertainty进行计算。文章来源地址https://www.toymoban.com/news/detail-791377.html

到了这里,关于时钟抖动(jitter)和时钟偏移(skew)的理解和建立/保持时间slack的计算的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[静态时序分析简明教程(二)] 基础知识:建立时间、保持时间、违例修复及时序分析路径](https://imgs.yssmx.com/Uploads/2024/02/421728-1.png)