2020.2

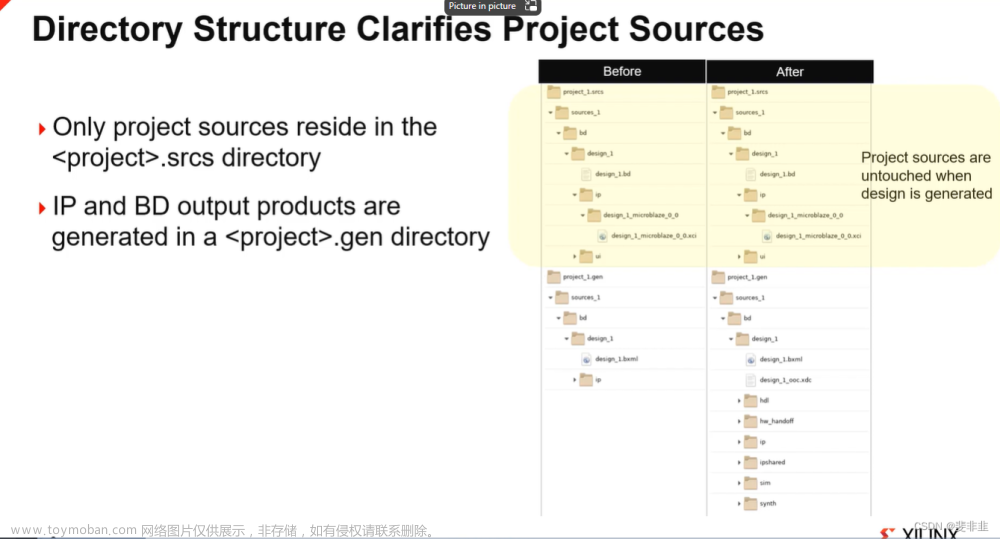

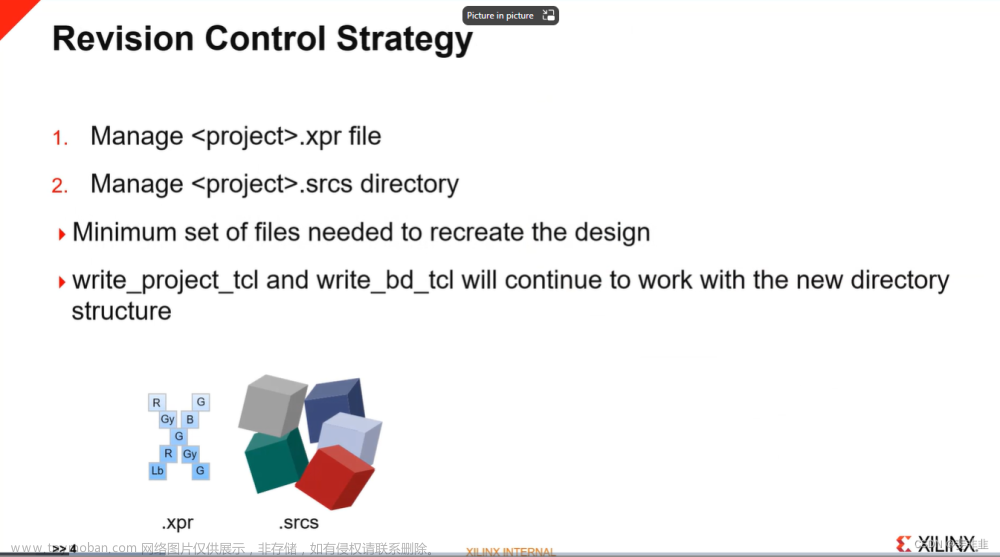

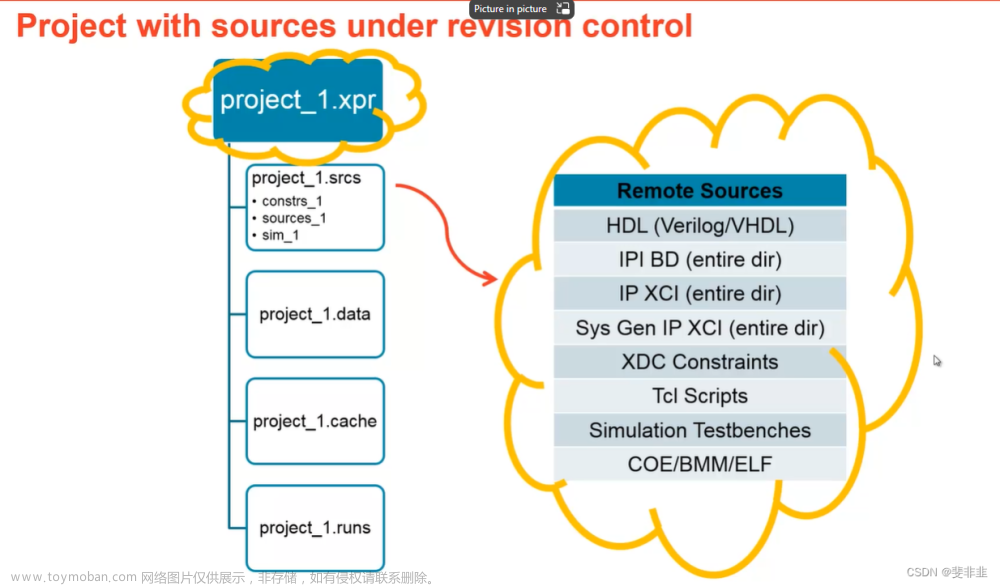

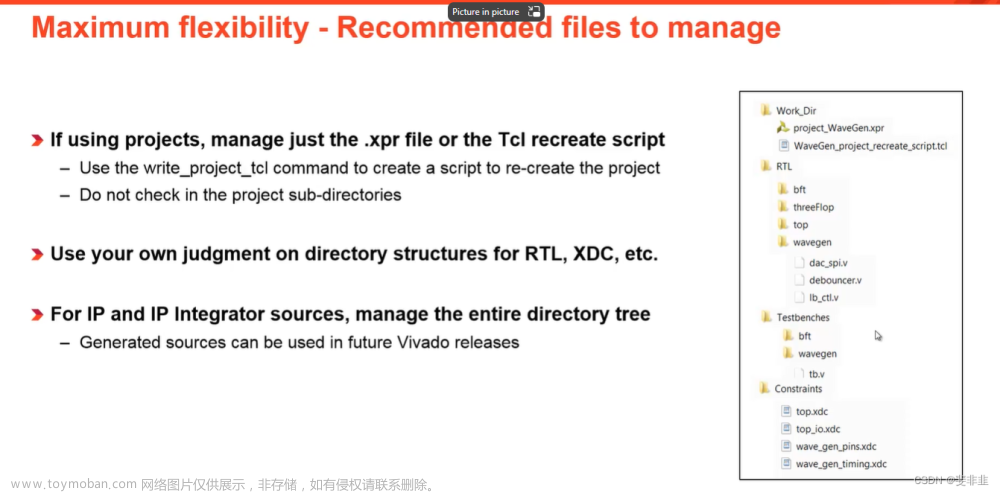

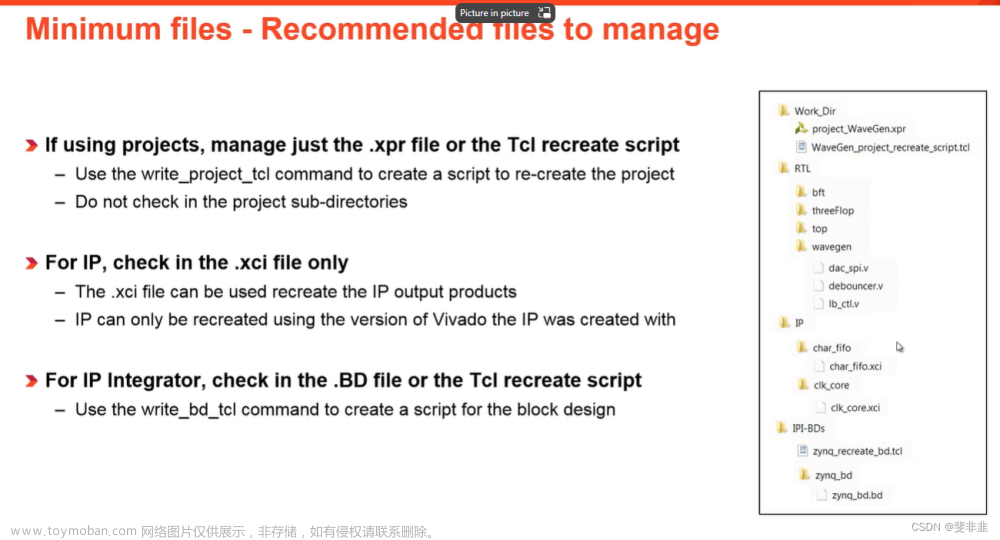

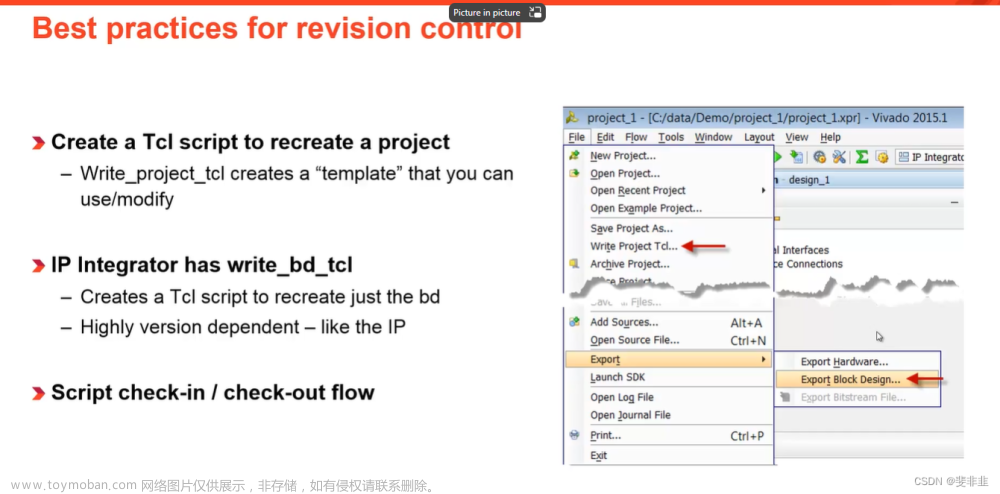

只需要git 管理 prj.xpr 和 prj.srcs/

https://china.xilinx.com/video/hardware/ip-revision-control.html

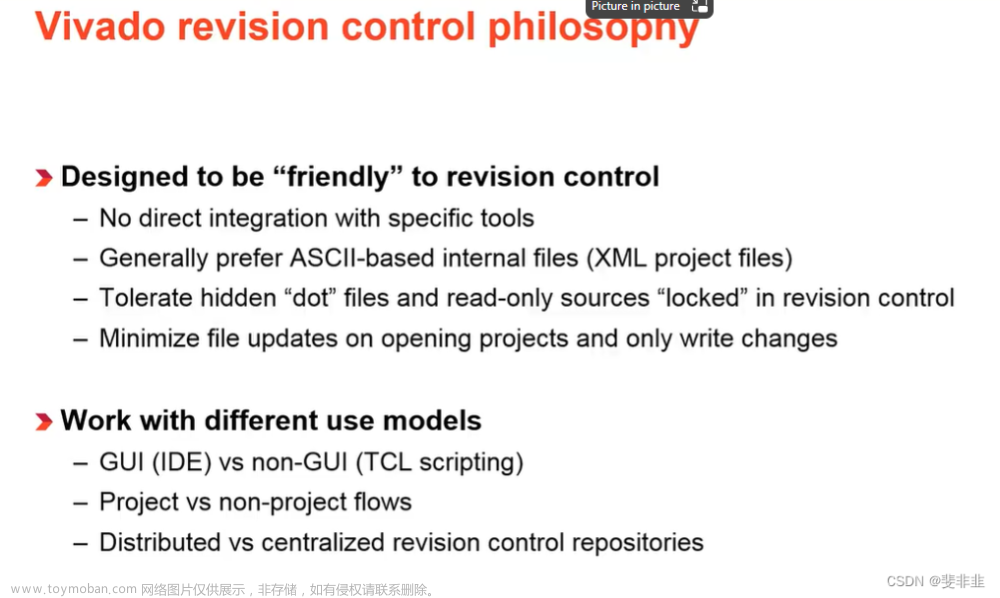

Using Vivado Design Suite with Revision Control

https://www.xilinx.com/video/hardware/vivado-design-suite-revision-control.html

http://www.xilinx.com/training

新-https://xilinxprod-catalog.netexam.com/

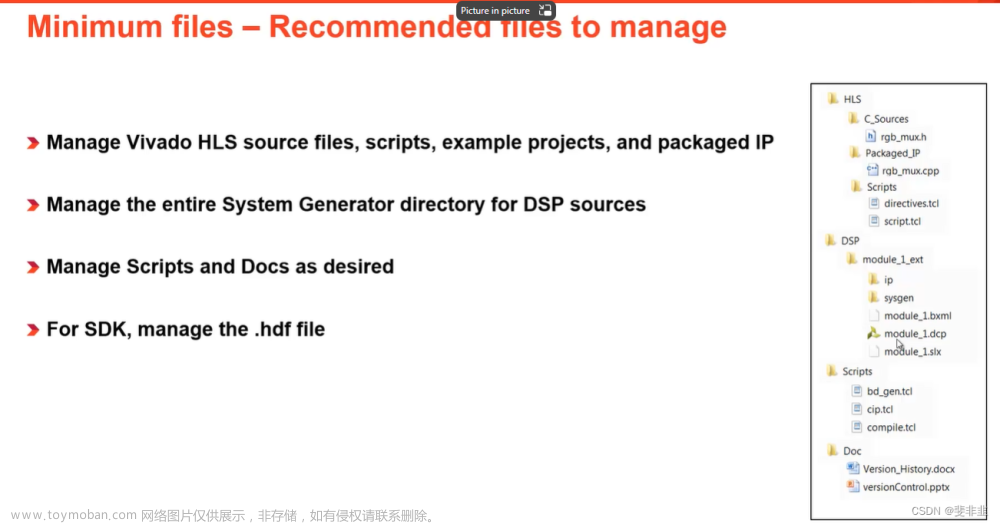

对于IP 保存所有文件;

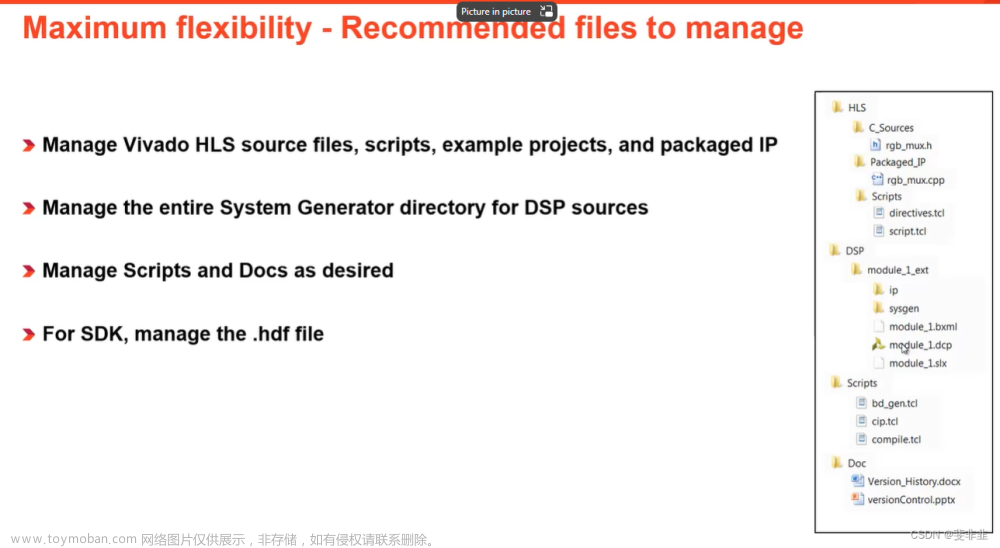

HLS

文章来源:https://www.toymoban.com/news/detail-791969.html

文章来源:https://www.toymoban.com/news/detail-791969.html

文章来源地址https://www.toymoban.com/news/detail-791969.html

文章来源地址https://www.toymoban.com/news/detail-791969.html

到了这里,关于vivado Revision Control的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!